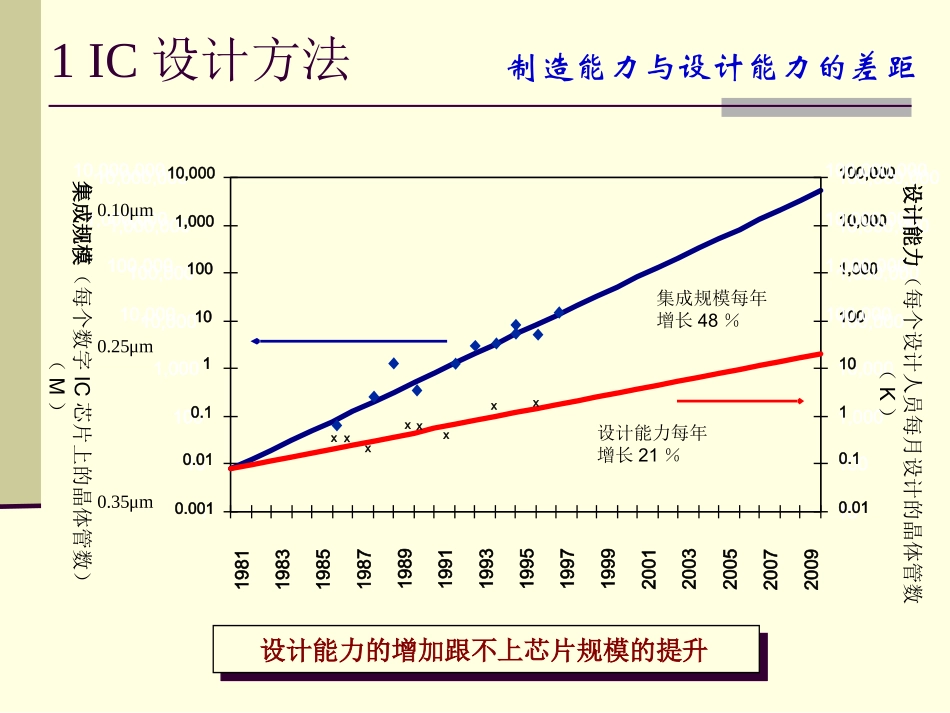

第8章设计方法、流程和工具集成电路设计系列庄奕琪主讲本章概要设计方法设计流程验证方法设计工具1IC设计方法制造能力与设计能力的差距1101001,00010,000100,0001,000,00010,000,000200319811983198519871989199119931995199719992001200520072009101001,00010,000100,0001,000,00010,000,000100,000,000xxxxxxxx10,0001,0001001010.10.010.0010.010.11101001,00010,000100,00010,000100,0001,000,00010,000,000100,0001,000,00010,000,000100,000,000集成规模(每个数字IC芯片上的晶体管数)(M)设计能力(每个设计人员每月设计的晶体管数(K)μm25.0μm35.0μm10.0集成规模每年增长48%设计能力每年增长21%设计能力的增加跟不上芯片规模的提升1K-5K10K-100K100K-1M1M-10M199119931995199719992001200...