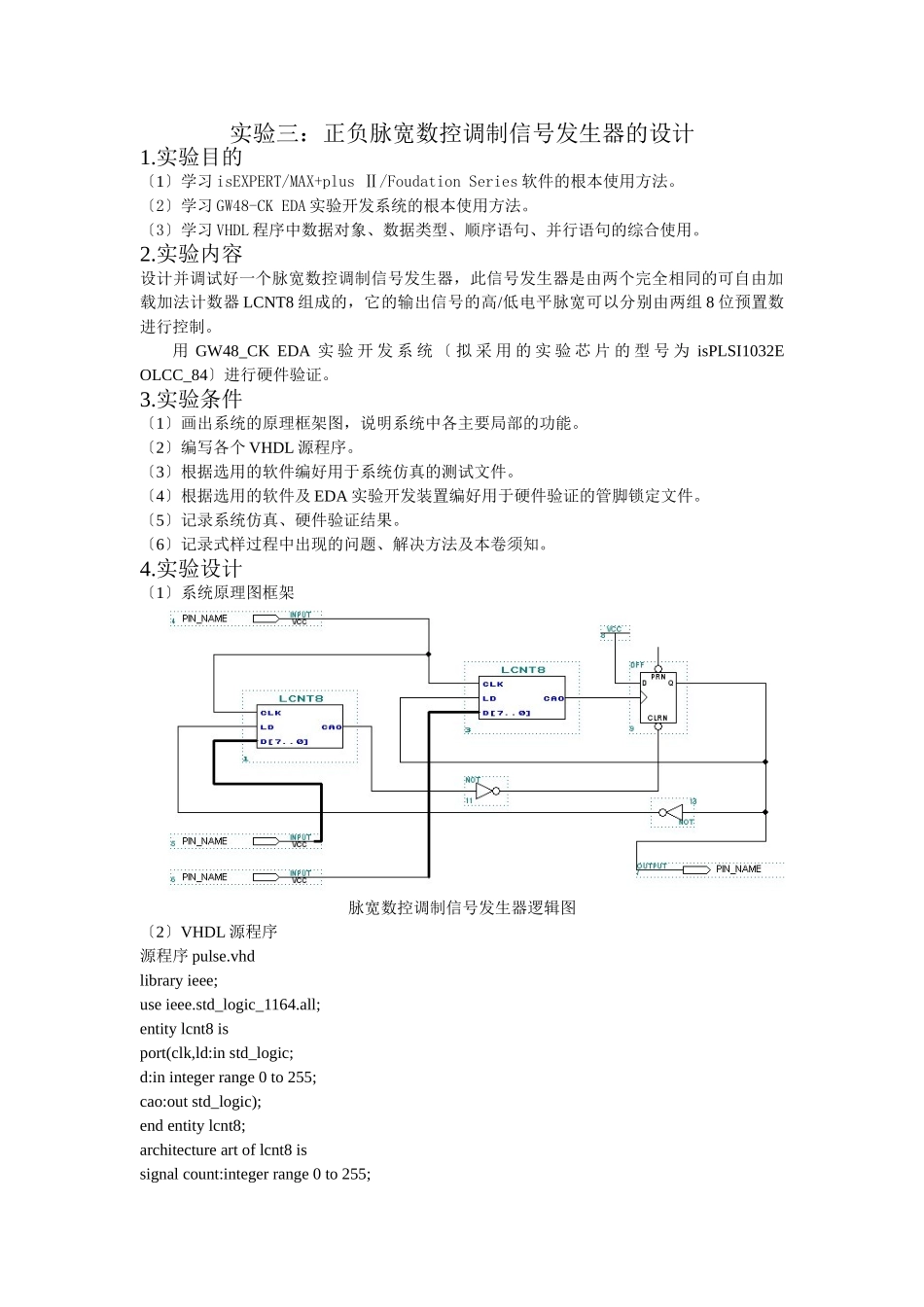

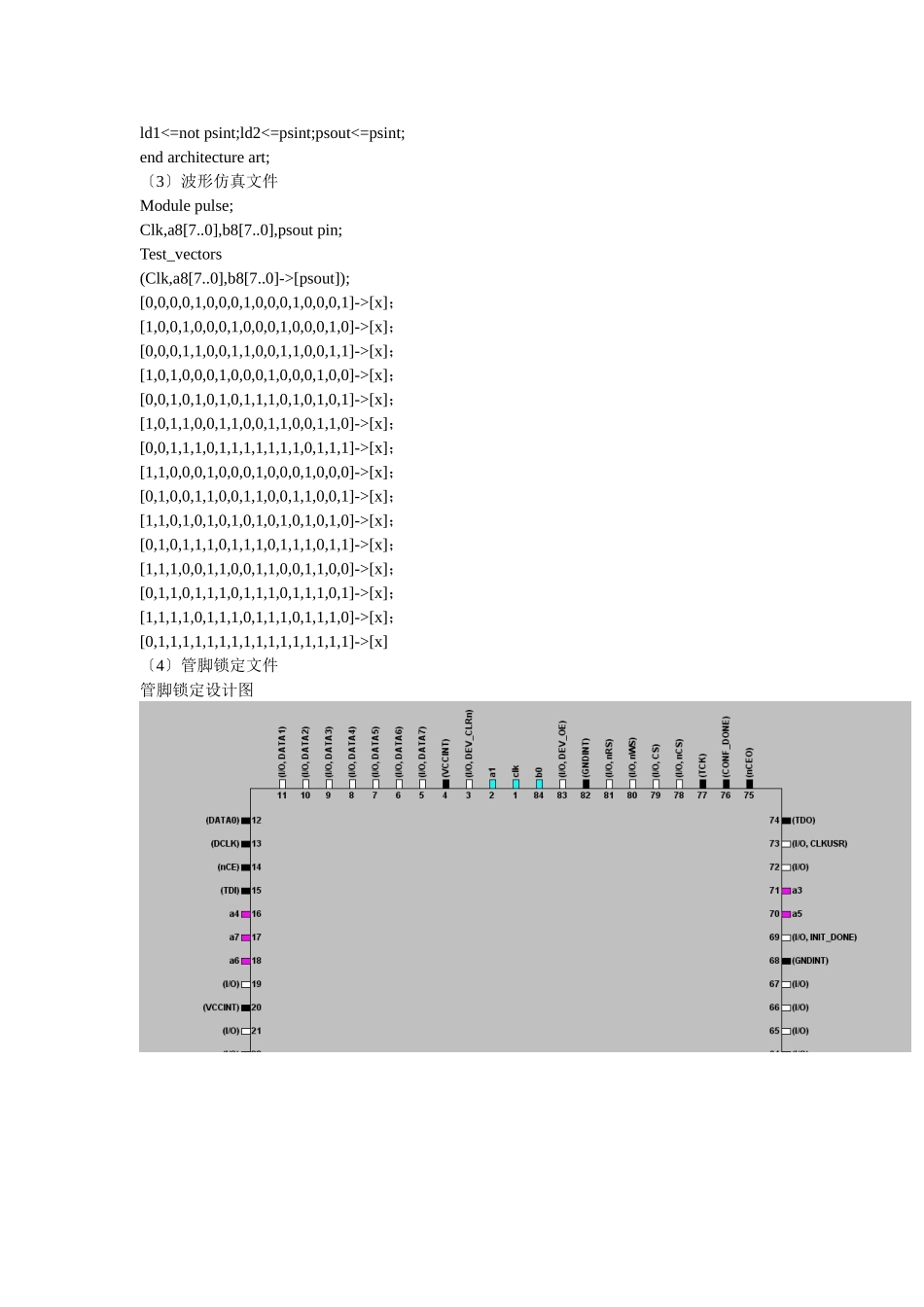

实验三:正负脉宽数控调制信号发生器的设计1.实验目的〔1〕学习isEXPERT/MAX+plusⅡ/FoudationSeries软件的根本使用方法。〔2〕学习GW48-CKEDA实验开发系统的根本使用方法。〔3〕学习VHDL程序中数据对象、数据类型、顺序语句、并行语句的综合使用。2.实验内容设计并调试好一个脉宽数控调制信号发生器,此信号发生器是由两个完全相同的可自由加载加法计数器LCNT8组成的,它的输出信号的高/低电平脉宽可以分别由两组8位预置数进行控制。用GW48_CKEDA实验开发系统〔拟采用的实验芯片的型号为isPLSI1032EOLCC_84〕进行硬件验证。3.实验条件〔1〕画出系统的原理框架图,说明系统中各主要局部的功能。〔2〕编写各个VHDL源程序。〔3〕根据选用的软件编好用于系统仿真的测试文件。〔4〕根据选用的软件及EDA实验开发装置编好用于硬件验证的管脚锁定文件。〔5〕记录系统仿真、硬件验证结果。〔6〕记录式样过程中出现的问题、解决方法及本卷须知。4.实验设计〔1〕系统原理图框架脉宽数控调制信号发生器逻辑图〔2〕VHDL源程序源程序pulse.vhdlibraryieee;useieee.std_logic_1164.all;entitylcnt8isport(clk,ld:instd_logic;d:inintegerrange0to255;cao:outstd_logic);endentitylcnt8;architectureartoflcnt8issignalcount:integerrange0to255;beginprocess(clk)isbeginifclk'eventandclk='1'thenifld='1'thencount<=d;elsecount<=count+1;endif;endif;endprocess;process(clk,count)isbeginifclk'eventandclk='1'thenifcount=255thencao<='1';elsecao<='0';endif;endif;endprocess;endarchitectureart;libraryieee;useieee.std_logic_1164.all;entitypulseisport(clk:instd_logic;a,b:instd_logic_vector(7downto0);psout:outstd_logic);endentitypulse;architectureartofpulseiscomponentlcnt8isport(clk,ld:instd_logic;d:instd_logic_vector(7downto0);cao:outstd_logic);endcomponentlcnt8;signalcao1,cao2:std_logic;signalld1,ld2:std_logic;signalpsint:std_logic;beginu1:lcnt8portmap(clk=>clk,ld=>ld1,d=>a,cao=>cao1);u2:lcnt8portmap(clk=>clk,ld=>ld2,d=>b,cao=>cao2);process(cao1,cao2)isbeginifcao1='1'thenpsint<='0';elsifcao2'eventandcao2='1'thenpsint<='1';endif;endprocess;ld1<=notpsint;ld2<=psint;psout<=psint;endarchitectureart;〔3〕波形仿真文件Modulepulse;Clk,a8[7..0],b8[7..0],psoutpin;Test_vectors(Clk,a8[7..0],b8[7..0]...