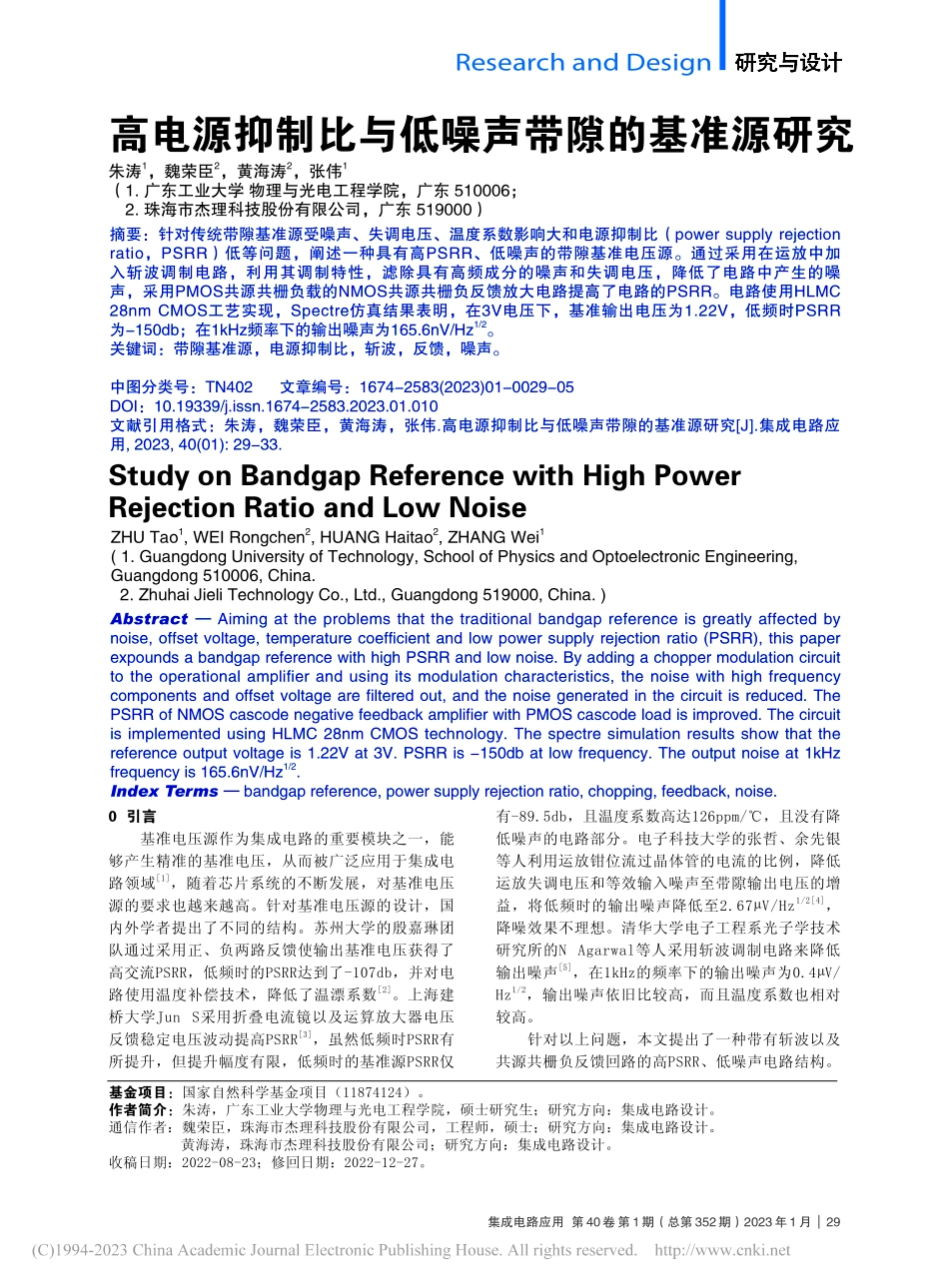

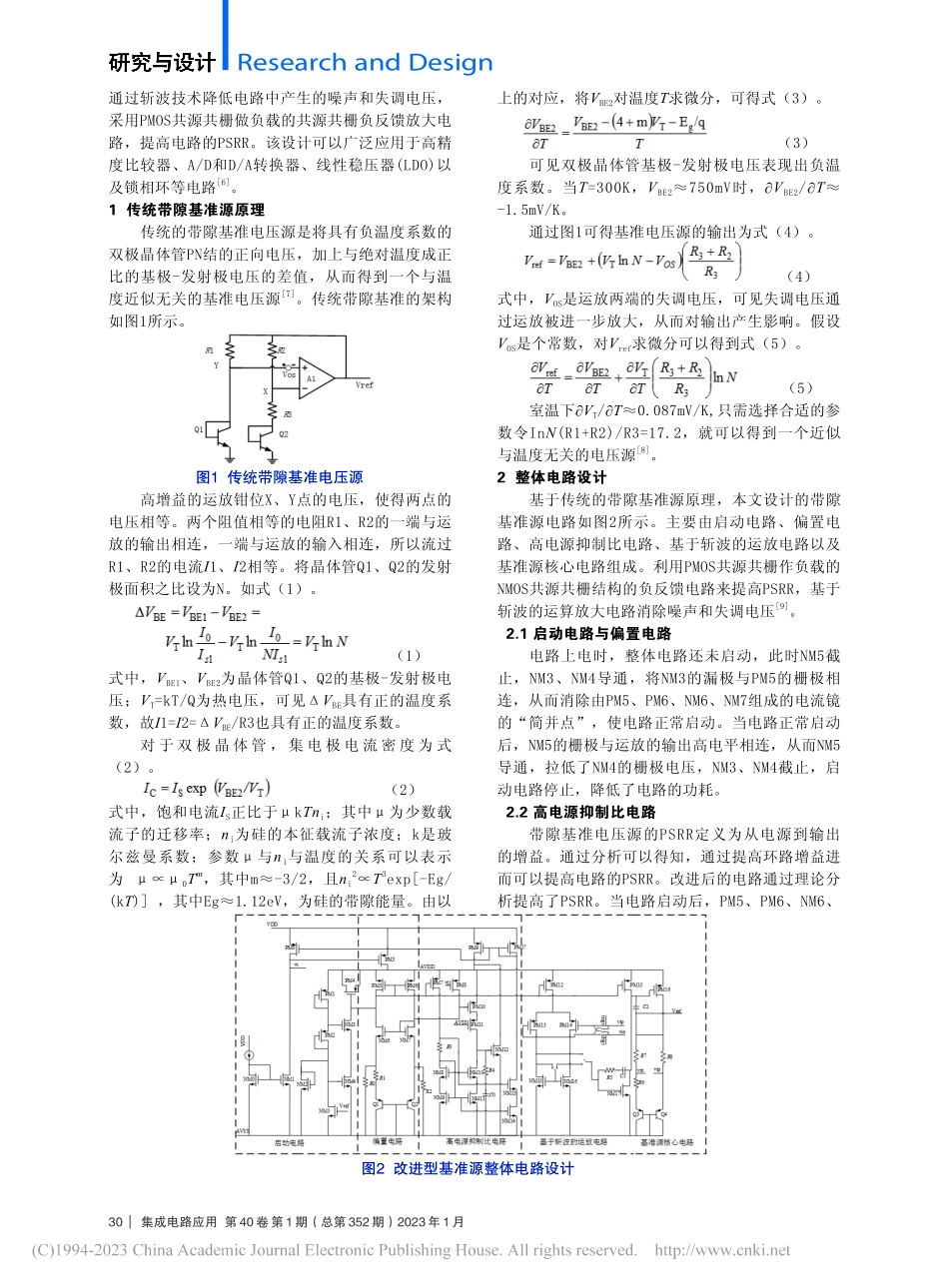

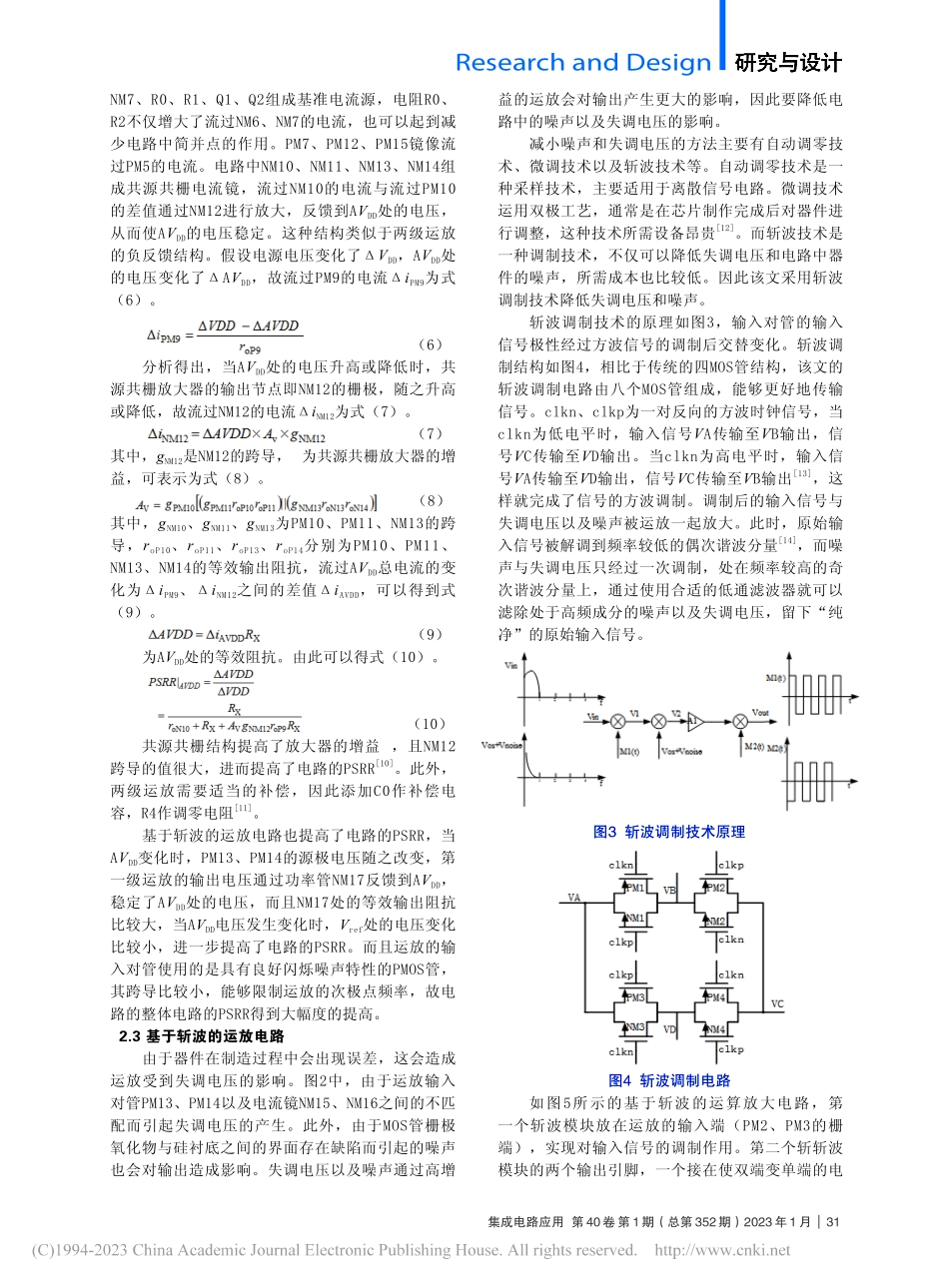

集成电路应用第40卷第1期(总第352期)2023年1月29ResearchandDesign研究与设计有-89.5db,且温度系数高达126ppm/℃,且没有降低噪声的电路部分。电子科技大学的张哲、余先银等人利用运放钳位流过晶体管的电流的比例,降低运放失调电压和等效输入噪声至带隙输出电压的增益,将低频时的输出噪声降低至2.67µV/Hz1/2[4],降噪效果不理想。清华大学电子工程系光子学技术研究所的NAgarwal等人采用斩波调制电路来降低输出噪声[5],在1kHz的频率下的输出噪声为0.4µV/Hz1/2,输出噪声依旧比较高,而且温度系数也相对较高。针对以上问题,本文提出了一种带有斩波以及共源共栅负反馈回路的高PSRR、低噪声电路结构。0引言基准电压源作为集成电路的重要模块之一,能够产生精准的基准电压,从而被广泛应用于集成电路领域[1],随着芯片系统的不断发展,对基准电压源的要求也越来越高。针对基准电压源的设计,国内外学者提出了不同的结构。苏州大学的殷嘉琳团队通过采用正、负两路反馈使输出基准电压获得了高交流PSRR,低频时的PSRR达到了-107db,并对电路使用温度补偿技术,降低了温漂系数[2]。上海建桥大学JunS采用折叠电流镜以及运算放大器电压反馈稳定电压波动提高PSRR[3],虽然低频时PSRR有所提升,但提升幅度有限,低频时的基准源PSRR仅基金项目:国家自然科学基金项目(11874124)。作者简介:朱涛,广东工业大学物理与光电工程学院,硕士研究生;研究方向:集成电路设计。通信作者:魏荣臣,珠海市杰理科技股份有限公司,工程师,硕士;研究方向:集成电路设计。黄海涛,珠海市杰理科技股份有限公司;研究方向:集成电路设计。收稿日期:2022-08-23;修回日期:2022-12-27。摘要:针对传统带隙基准源受噪声、失调电压、温度系数影响大和电源抑制比(powersupplyrejectionratio,PSRR)低等问题,阐述一种具有高PSRR、低噪声的带隙基准电压源。通过采用在运放中加入斩波调制电路,利用其调制特性,滤除具有高频成分的噪声和失调电压,降低了电路中产生的噪声,采用PMOS共源共栅负载的NMOS共源共栅负反馈放大电路提高了电路的PSRR。电路使用HLMC28nmCMOS工艺实现,Spectre仿真结果表明,在3V电压下,基准输出电压为1.22V,低频时PSRR为-150db;在1kHz频率下的输出噪声为165.6nV/Hz1/2。关键词:带隙基准源,电源抑制比,斩波,反馈,噪声。中图分类号:TN402文章编号:1674-2583(2023)01-0029-05DOI:10.19339/j.issn.1674-2583.2023.01.010文献引用格式:...