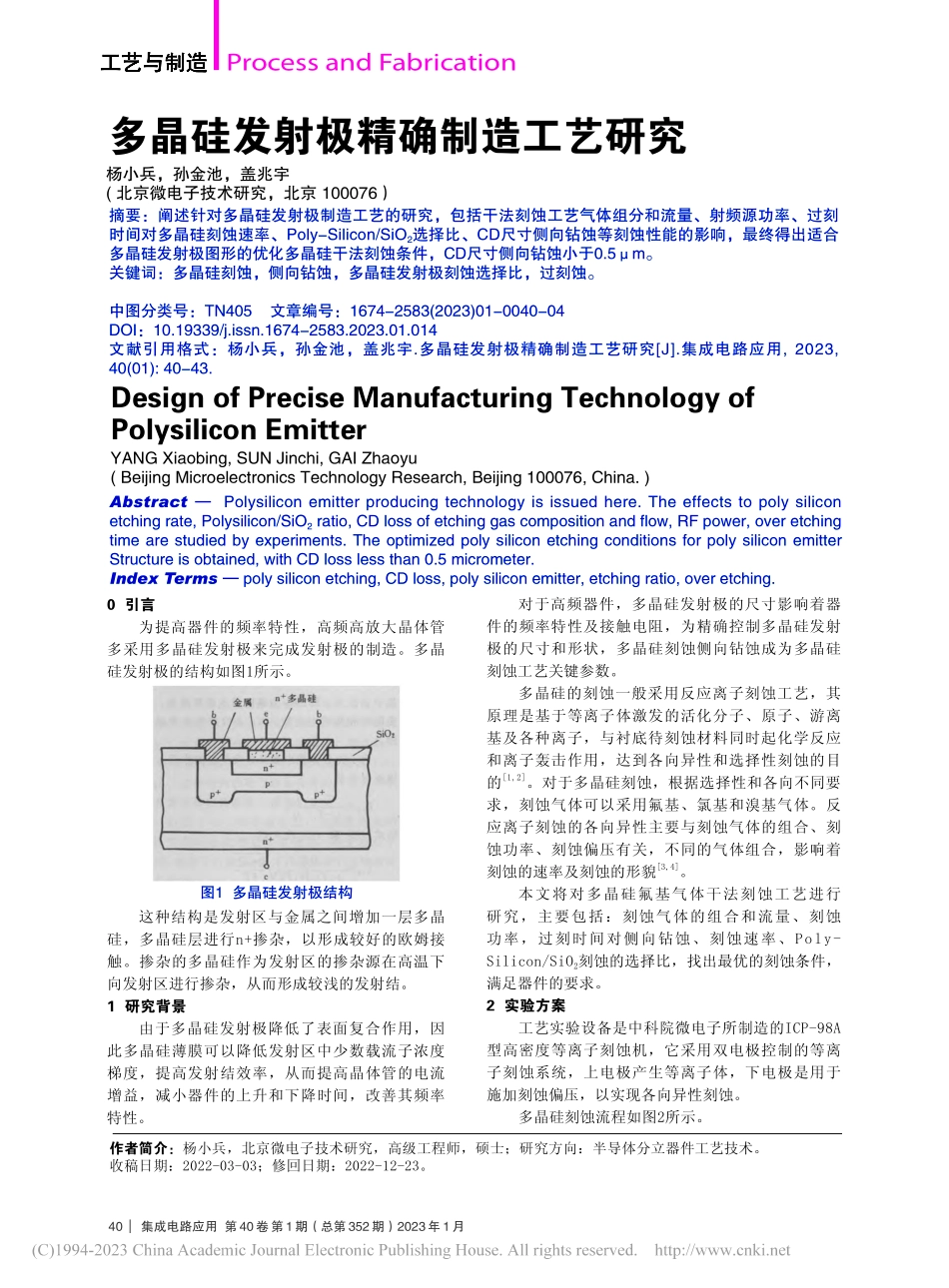

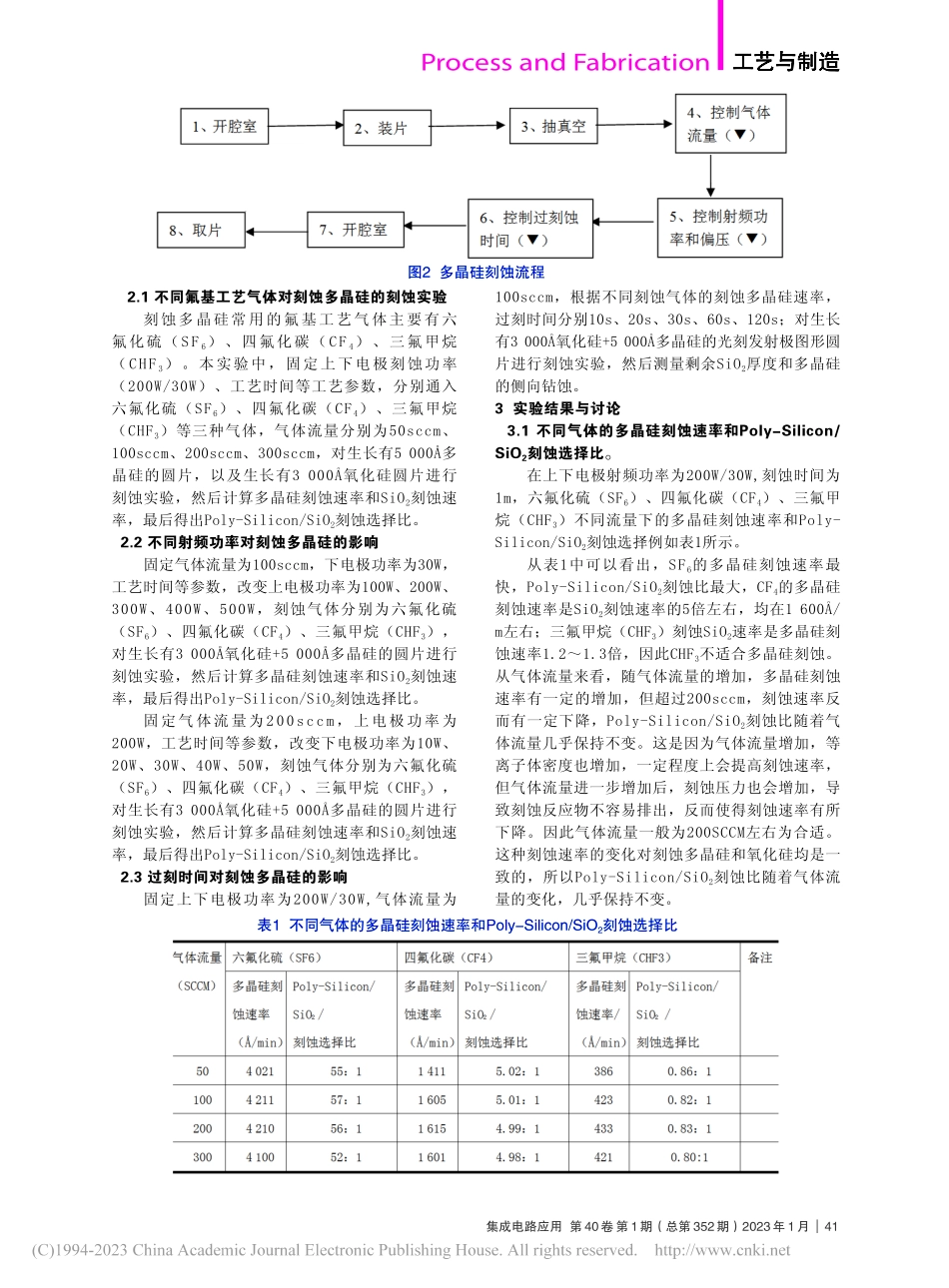

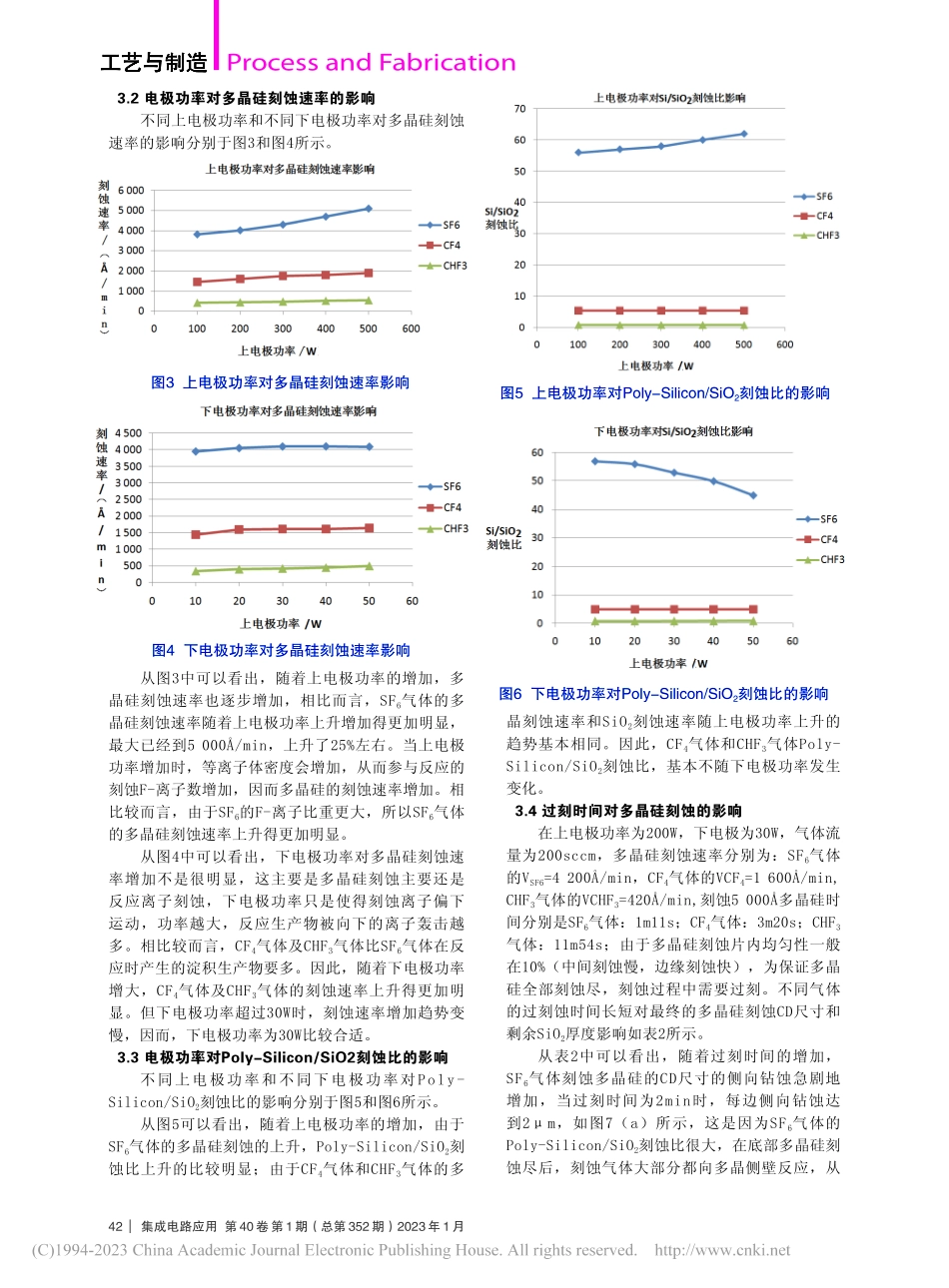

40集成电路应用第40卷第1期(总第352期)2023年1月ProcessandFabrication工艺与制造摘要:阐述针对多晶硅发射极制造工艺的研究,包括干法刻蚀工艺气体组分和流量、射频源功率、过刻时间对多晶硅刻蚀速率、Poly-Silicon/SiO2选择比、CD尺寸侧向钻蚀等刻蚀性能的影响,最终得出适合多晶硅发射极图形的优化多晶硅干法刻蚀条件,CD尺寸侧向钻蚀小于0.5μm。关键词:多晶硅刻蚀,侧向钻蚀,多晶硅发射极刻蚀选择比,过刻蚀。中图分类号:TN405文章编号:1674-2583(2023)01-0040-04DOI:10.19339/j.issn.1674-2583.2023.01.014文献引用格式:杨小兵,孙金池,盖兆宇.多晶硅发射极精确制造工艺研究[J].集成电路应用,2023,40(01):40-43.对于高频器件,多晶硅发射极的尺寸影响着器件的频率特性及接触电阻,为精确控制多晶硅发射极的尺寸和形状,多晶硅刻蚀侧向钻蚀成为多晶硅刻蚀工艺关键参数。多晶硅的刻蚀一般采用反应离子刻蚀工艺,其原理是基于等离子体激发的活化分子、原子、游离基及各种离子,与衬底待刻蚀材料同时起化学反应和离子轰击作用,达到各向异性和选择性刻蚀的目的[1,2]。对于多晶硅刻蚀,根据选择性和各向不同要求,刻蚀气体可以采用氟基、氯基和溴基气体。反应离子刻蚀的各向异性主要与刻蚀气体的组合、刻蚀功率、刻蚀偏压有关,不同的气体组合,影响着刻蚀的速率及刻蚀的形貌[3,4]。本文将对多晶硅氟基气体干法刻蚀工艺进行研究,主要包括:刻蚀气体的组合和流量、刻蚀功率,过刻时间对侧向钻蚀、刻蚀速率、Poly-Silicon/SiO2刻蚀的选择比,找出最优的刻蚀条件,满足器件的要求。2实验方案工艺实验设备是中科院微电子所制造的ICP-98A型高密度等离子刻蚀机,它采用双电极控制的等离子刻蚀系统,上电极产生等离子体,下电极是用于施加刻蚀偏压,以实现各向异性刻蚀。多晶硅刻蚀流程如图2所示。0引言为提高器件的频率特性,高频高放大晶体管多采用多晶硅发射极来完成发射极的制造。多晶硅发射极的结构如图1所示。这种结构是发射区与金属之间增加一层多晶硅,多晶硅层进行n+掺杂,以形成较好的欧姆接触。掺杂的多晶硅作为发射区的掺杂源在高温下向发射区进行掺杂,从而形成较浅的发射结。1研究背景由于多晶硅发射极降低了表面复合作用,因此多晶硅薄膜可以降低发射区中少数载流子浓度梯度,提高发射结效率,从而提高晶体管的电流增益,减小器件的上升和下降时间,改善其频率特性。多晶硅发射极精确制造工艺研究杨小兵,孙金池,盖兆宇(北京微...