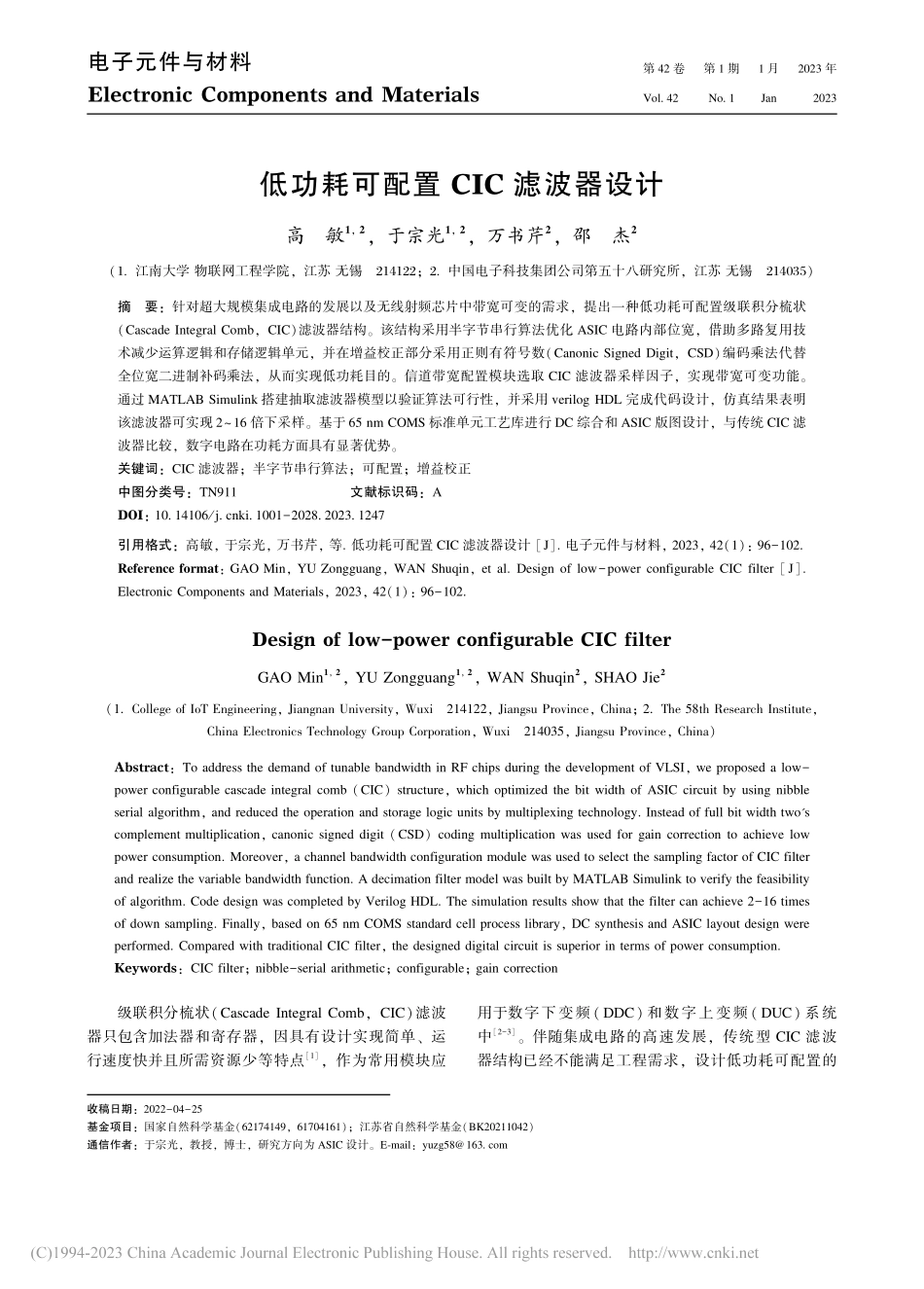

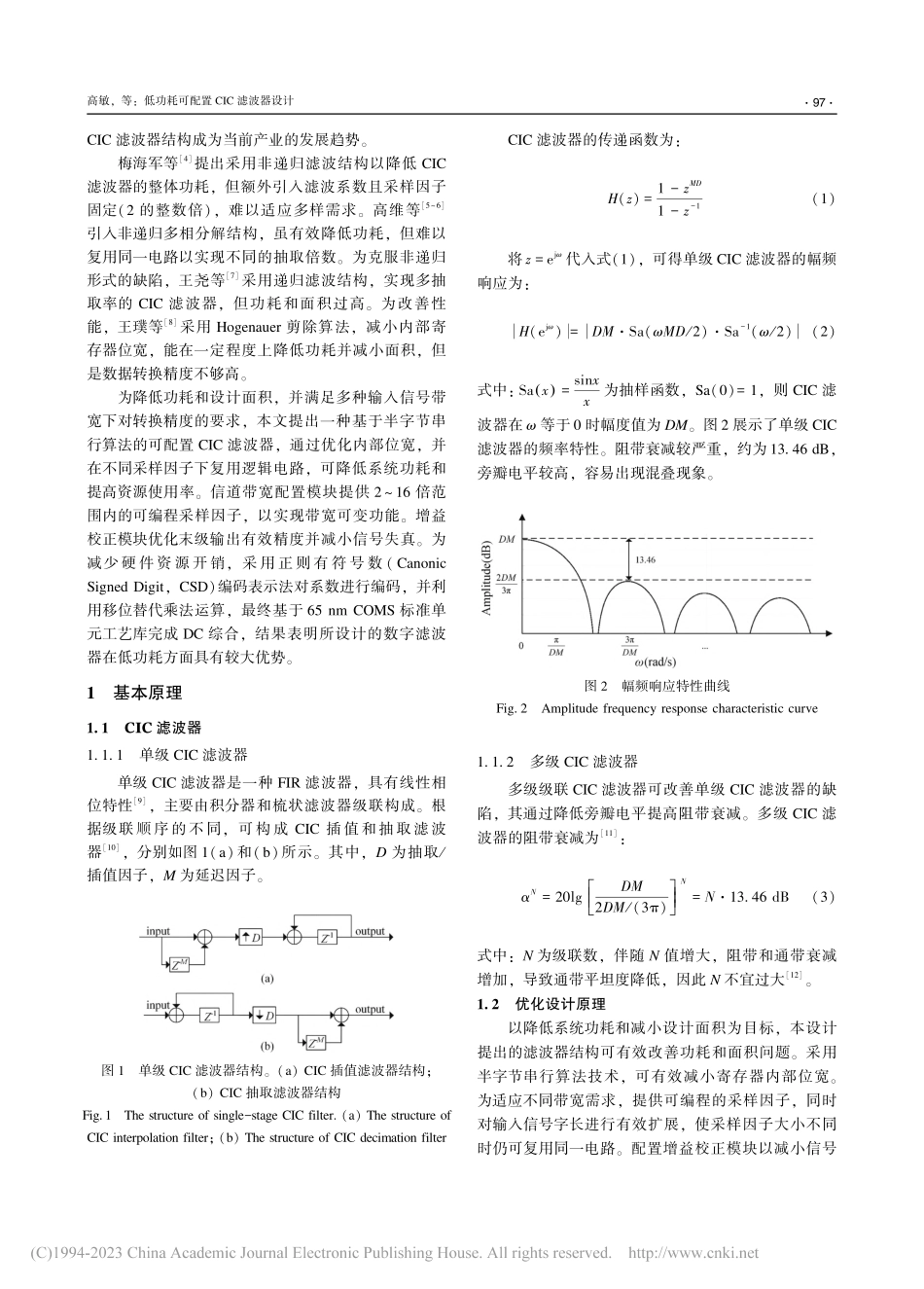

收稿日期:2022-04-25基金项目:国家自然科学基金(62174149,61704161);江苏省自然科学基金(BK20211042)通信作者:于宗光,教授,博士,研究方向为ASIC设计。E⁃mail:yuzg58@163.com电子元件与材料ElectronicComponentsandMaterials第42卷Vol.42第1期No.11月Jan2023年2023低功耗可配置CIC滤波器设计高敏1,2,于宗光1,2,万书芹2,邵杰2(1.江南大学物联网工程学院,江苏无锡214122;2.中国电子科技集团公司第五十八研究所,江苏无锡214035)摘要:针对超大规模集成电路的发展以及无线射频芯片中带宽可变的需求,提出一种低功耗可配置级联积分梳状(CascadeIntegralComb,CIC)滤波器结构。该结构采用半字节串行算法优化ASIC电路内部位宽,借助多路复用技术减少运算逻辑和存储逻辑单元,并在增益校正部分采用正则有符号数(CanonicSignedDigit,CSD)编码乘法代替全位宽二进制补码乘法,从而实现低功耗目的。信道带宽配置模块选取CIC滤波器采样因子,实现带宽可变功能。通过MATLABSimulink搭建抽取滤波器模型以验证算法可行性,并采用verilogHDL完成代码设计,仿真结果表明该滤波器可实现2~16倍下采样。基于65nmCOMS标准单元工艺库进行DC综合和ASIC版图设计,与传统CIC滤波器比较,数字电路在功耗方面具有显著优势。关键词:CIC滤波器;半字节串行算法;可配置;增益校正中图分类号:TN911文献标识码:ADOI:10.14106/j.cnki.1001-2028.2023.1247引用格式:高敏,于宗光,万书芹,等.低功耗可配置CIC滤波器设计[J].电子元件与材料,2023,42(1):96-102.Referenceformat:GAOMin,YUZongguang,WANShuqin,etal.Designoflow-powerconfigurableCICfilter[J].ElectronicComponentsandMaterials,2023,42(1):96-102.Designoflow-powerconfigurableCICfilterGAOMin1,2,YUZongguang1,2,WANShuqin2,S...