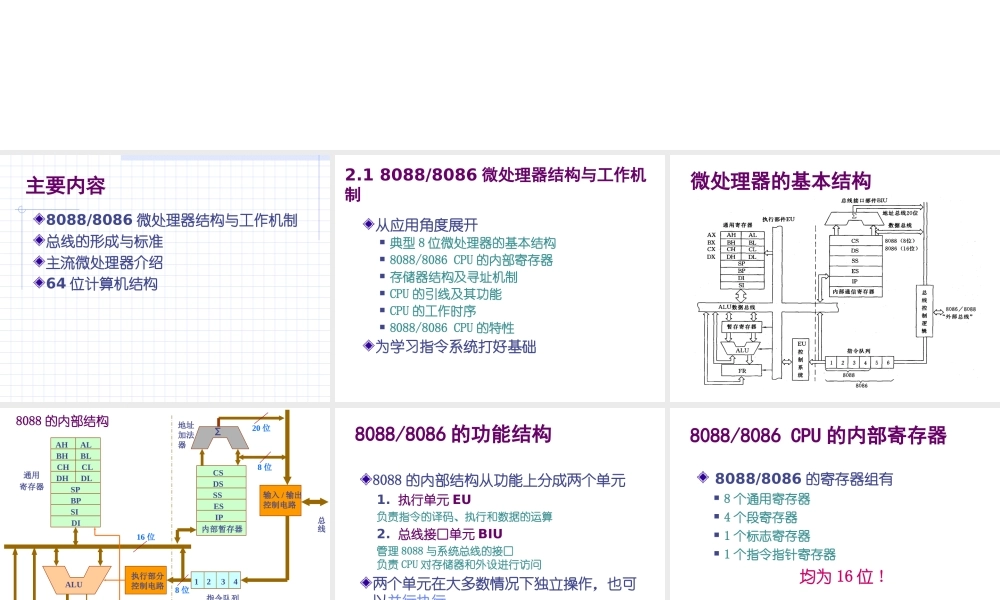

第2章微处理器与总线微机原理与接口技术主要内容8088/8086微处理器结构与工作机制总线的形成与标准主流微处理器介绍64位计算机结构从应用角度展开典型8位微处理器的基本结构8088/8086CPU的内部寄存器存储器结构及寻址机制CPU的引线及其功能CPU的工作时序8088/8086CPU的特性为学习指令系统打好基础2.18088/8086微处理器结构与工作机制微处理器的基本结构8088的内部结构1234内部暂存器IPESSSDSCS输入/输出控制电路总线执行部分控制电路∑ALU标志寄存器AHALBHBLCHCLDHDLSPBPSIDI通用寄存器地址加法器指令队列执行部件(EU)总线接口部件(BIU)16位20位8位8位8088/8086的功能结构8088的内部结构从功能上分成两个单元1.执行单元EU负责指令的译码、执行和数据的运算2.总线接口单元BIU管理8088与系统总线的接口负责CPU对存储器和外设进行访问两个单元在大多数情况下独立操作,也可以并行执行8088/8086CPU的内部寄存器8088/8086的寄存器组有8个通用寄存器4个段寄存器1个标志寄存器1个指令指针寄存器均为16位!1.通用寄存器8088有8个通用的16位寄存器(1)数据寄存器:AXBXCXDX(2)变址寄存器:SIDI(3)指针寄存器:BPSP4个数据寄存器可分成高8位和低8位两个独立的寄存器:AX:AHALBX:BHBLCX:CHCLDX:DHDL(1)数据寄存器AX:累加器(Accumulator)使用频度最高,用于算术、逻辑运算以及与外设传送信息等。BX:基址寄存器(BaseaddressRegister)常用于存放存储器地址。CX:计数器(Counter)循环、串操作等指令中的隐含计数器。DX:数据寄存器(Dataregister)存放双字长数据的高16位,或外设端口地址。(2)变址寄存器16位变址寄存器SI和DI常用于存储器变址寻址方式时提供地址SI:源地址寄存器(SourceIndex)DI:目的地址寄存器(DestinationIndex)在串操作类指令中,SI、DI有特殊用法(3)指针寄存器指针寄存器用于寻址内存堆栈内的数据SP:堆栈指针寄存器(StackPointer),指示堆栈段栈顶的位置(偏移地址)BP:基址指针寄存器(BasePointer),表示数据在堆栈段中的基地址SP和BP寄存器与SS段寄存器联合使用以确定堆栈段中的存储单元地址堆栈(Stack)是主存中一个特殊的区域,采用“先进后出”或“后进先出”存取操作方式。用8088/8086形成的微机系统中,堆栈区域被称为堆栈段。2.指令指针寄存器IP(InstructionPointer):指令指针寄存器,指示主存储器指令的位置随着指令的执行,IP将自动修改以指示下一条...