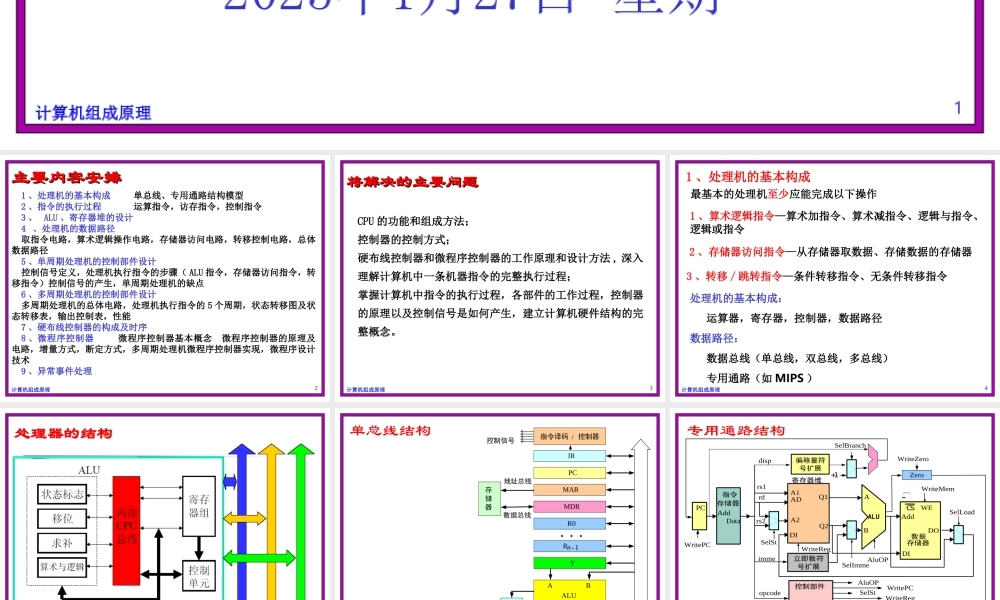

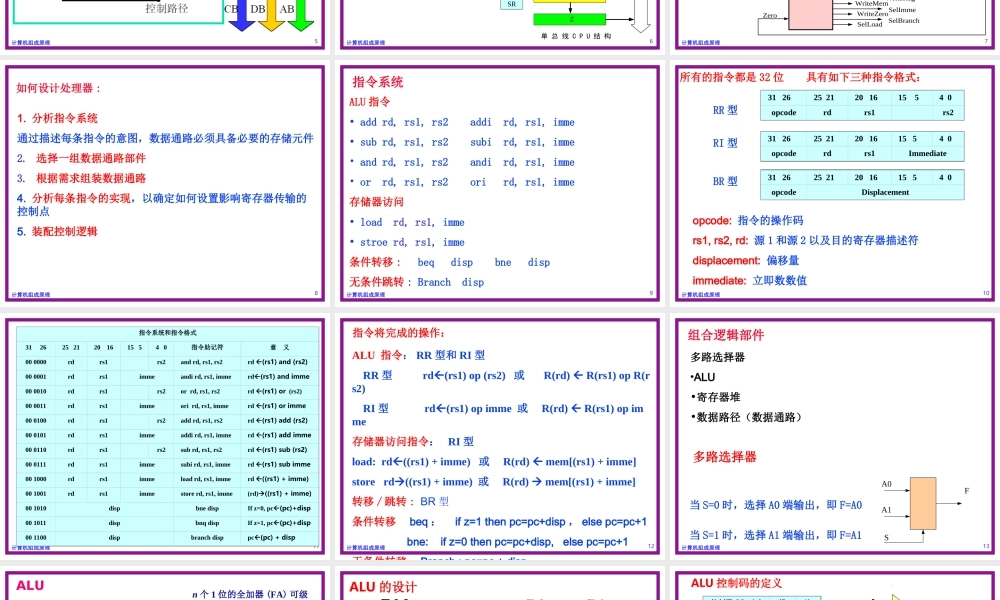

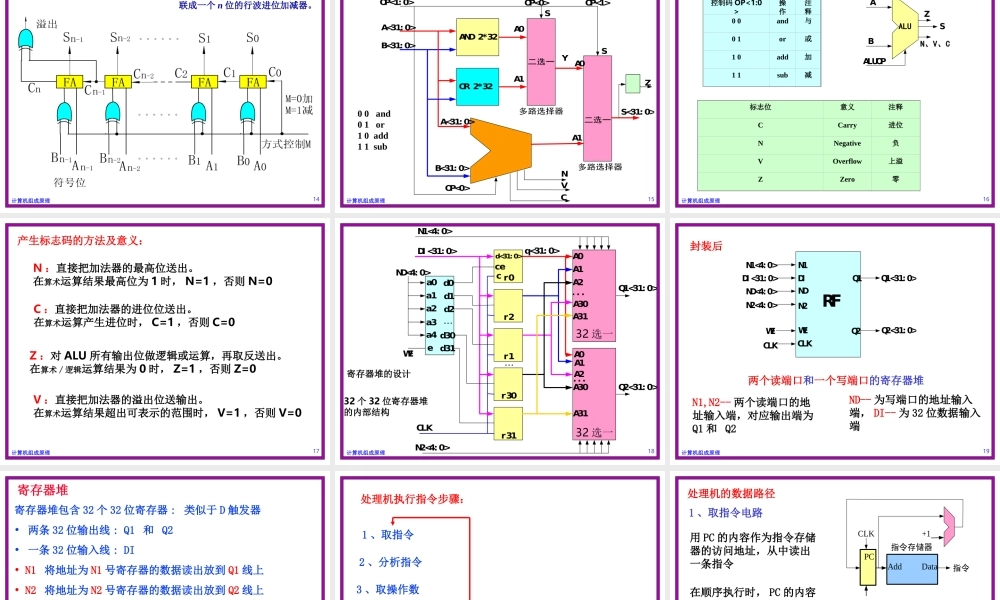

计算机组成原理1计算机组成原理计算机组成原理2025年1月27日星期一处理机设计计算机组成原理21、处理机的基本构成单总线、专用通路结构模型2、指令的执行过程运算指令,访存指令,控制指令3、ALU、寄存器堆的设计4、处理机的数据路径取指令电路,算术逻辑操作电路,存储器访问电路,转移控制电路,总体数据路径5、单周期处理机的控制部件设计控制信号定义,处理机执行指令的步骤(ALU指令,存储器访问指令,转移指令)控制信号的产生,单周期处理机的缺点6、多周期处理机的控制部件设计多周期处理机的总体电路,处理机执行指令的5个周期,状态转移图及状态转移表,输出控制表,性能7、硬布线控制器的构成及时序8、微程序控制器微程序控制器基本概念微程序控制器的原理及电路,增量方式,断定方式,多周期处理机微程序控制器实现,微程序设计技术9、异常事件处理主要内容安排主要内容安排计算机组成原理3将解决的主要问题将解决的主要问题CPU的功能和组成方法;控制器的控制方式;硬布线控制器和微程序控制器的工作原理和设计方法,深入理解计算机中一条机器指令的完整执行过程;掌握计算机中指令的执行过程,各部件的工作过程,控制器的原理以及控制信号是如何产生,建立计算机硬件结构的完整概念。计算机组成原理41、处理机的基本构成最基本的处理机至少应能完成以下操作1、算术逻辑指令—算术加指令、算术减指令、逻辑与指令、逻辑或指令2、存储器访问指令—从存储器取数据、存储数据的存储器3、转移/跳转指令—条件转移指令、无条件转移指令处理机的基本构成:运算器,寄存器,控制器,数据路径数据路径:数据总线(单总线,双总线,多总线)专用通路(如MIPS)计算机组成原理5处理器的结构计算机组成原理6单总线结构单总线CPU结构指令译码/控制器IRPCMARMDRR0YSRZABALU存储器控制信号地址总线数据总线Rn-1...计算机组成原理7专用通路结构ALUPC寄存器堆rs2rdWritePCSelStAluOPWriteMemSelLoaddispWriteRegrs1SelBranchWriteZero+1ZeroZeroimmeSelImmeopcodeAluOPWritePCSelStWriteRegWriteMemSelImmeWriteZeroSelBranchSelLoad控制部件A1Q1Q2DIADA2偏移量符号扩展立即数符号扩展指令存储器AddData数据存储器AddDODIWECSAB计算机组成原理81.分析指令系统通过描述每条指令的意图,数据通路必须具备必要的存储元件2.选择一组数据通路部件3.根据需求组装数据通路4.分析每条指令的实现,以确定如何设置影响寄存器传输的控制点5.装配控制逻辑如何设计处...