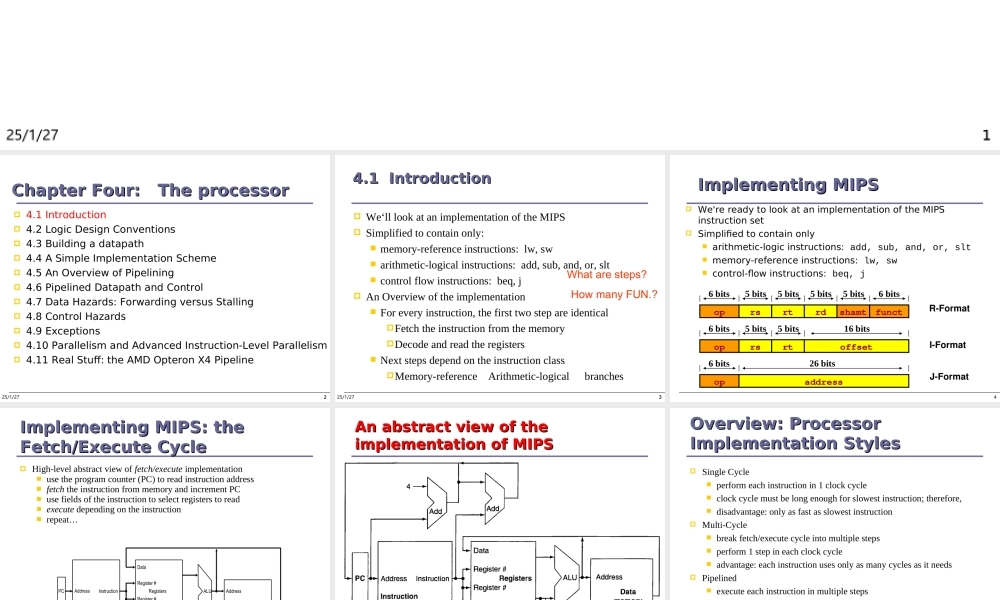

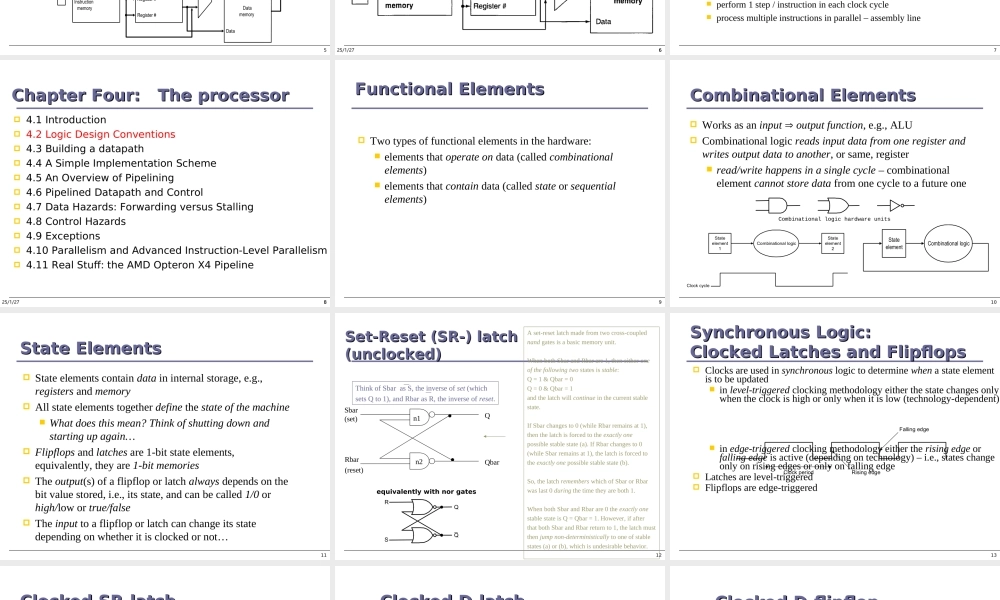

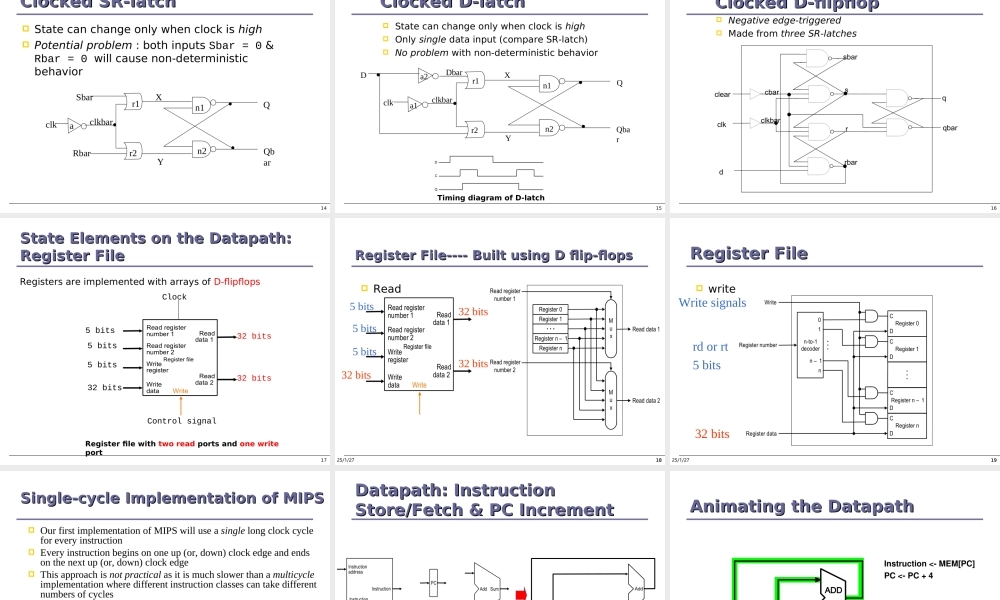

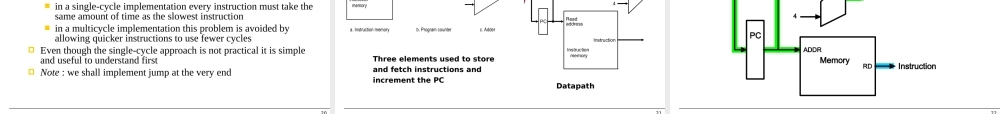

1ComputerComputerOrganization&DesignOrganization&Design——TheHardware/SoftwareInterfaceTheHardware/SoftwareInterface25/1/271Theprocessor2ChapterFour:TheprocessorChapterFour:Theprocessor4.1Introduction4.2LogicDesignConventions4.3Buildingadatapath4.4ASimpleImplementationScheme4.5AnOverviewofPipelining4.6PipelinedDatapathandControl4.7DataHazards:ForwardingversusStalling4.8ControlHazards4.9Exceptions4.10ParallelismandAdvancedInstruction-LevelParallelism4.11RealStuff:theAMDOpteronX4Pipeline25/1/2723We‘lllookatanimplementationoftheMIPSSimplifiedtocontainonly:memory-referenceinstructions:lw,swarithmetic-logicalinstructions:add,sub,and,or,sltcontrolflowinstructions:beq,jAnOverviewoftheimplementationForeveryinstruction,thefirsttwostepareidenticalFetchtheinstructionfromthememoryDecodeandreadtheregistersNextstepsdependontheinstructionclassMemory-referenceArithmetic-logicalbranches4.1Introduction4.1IntroductionWhataresteps?HowmanyFUN.?25/1/2734We'rereadytolookatanimplementationoftheMIPSinstructionsetSimplifiedtocontainonlyarithmetic-logicinstructions:add,sub,and,or,sltmemory-referenceinstructions:lw,swcontrol-flowinstructions:beq,jImplementingMIPSImplementingMIPSoprsrtoffset6bits5bits5bits16bitsoprsrtrdfunctshamt6bits5bits5bits5bits5bits6bitsR-FormatI-Formatopaddress6bits26bitsJ-Format5High-levelabstractviewoffetch/executeimplementationusetheprogramcounter(PC)toreadinstructionaddressfetchtheinstructionfrommemoryandincrementPCusefieldsoftheinstructiontoselectregisterstoreadexecutedependingontheinstructionrepeat…ImplementingMIPS:theImplementingMIPS:theFetch/ExecuteCycleFetch/ExecuteCycleRegistersRegister#DataRegister#DatamemoryAddressDataRegister#PCInstructionALUInstructionmemoryAddress6AnabstractviewoftheAnabstractviewoftheimplementationofMIPSimplementationofMIPS25/1/2767Overview:ProcessorOverview:ProcessorImplementationStylesImplementationStylesSingleCycleperformeachinstructionin1clockcycleclockcyclem...