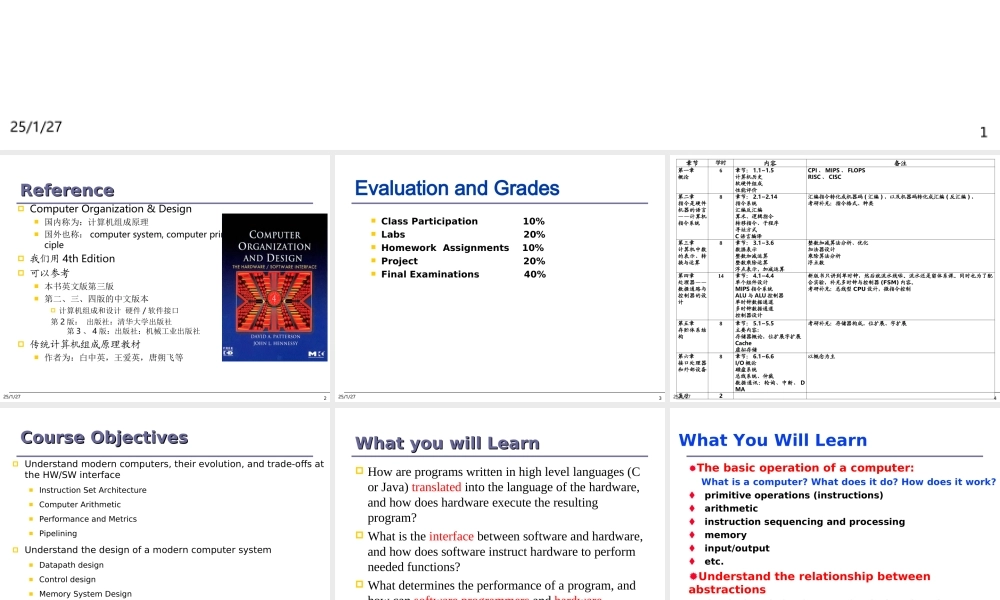

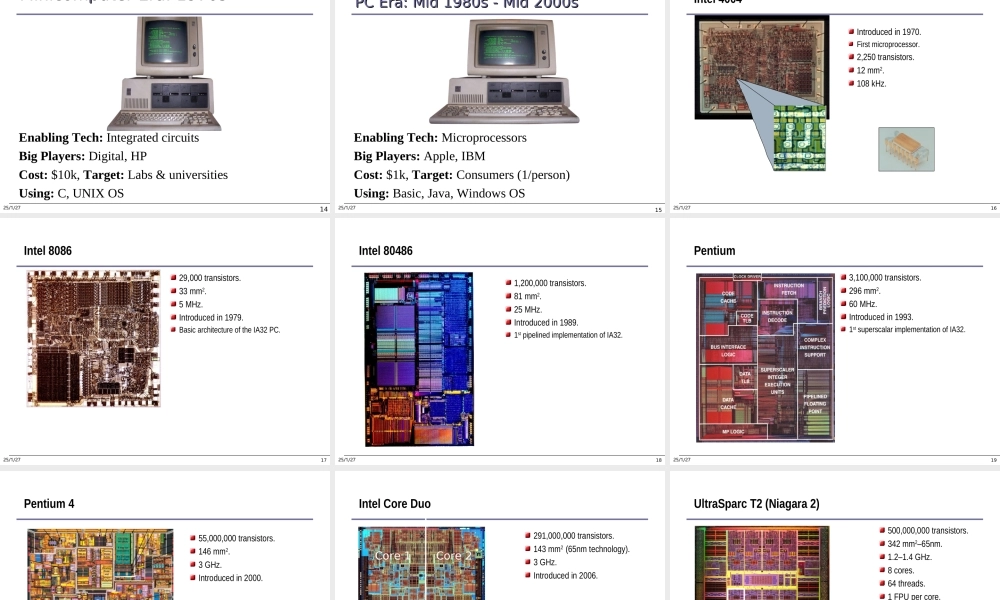

ComputerComputerOrganization&DesignOrganization&Design——TheHardware/SoftwareInterfaceTheHardware/SoftwareInterface25/1/271ReferenceReferenceComputerOrganization&Design国内称为:计算机组成原理国外也称:computersystem,computerprinciple我们用4thEdition可以参考本书英文版第三版第二、三、四版的中文版本计算机组成和设计硬件/软件接口第2版:出版社:清华大学出版社第3、4版:出版社:机械工业出版社传统计算机组成原理教材作者为:白中英,王爱英,唐朔飞等25/1/272EvaluationandGradesClassParticipation10%Labs20%HomeworkAssignments10%Project20%FinalExaminations40%25/1/273章节学时内容备注第一章概论6章节:1.1~1.5计算机历史软硬件组成性能评价CPI、MIPS、FLOPSRISC、CISC第二章指令是硬件机器的语言——计算机指令系统8章节:2.1~2.14指令系统汇编反汇编算术、逻辑指令转移指令、子程序寻址方式C语言编译汇编指令转化成机器码(汇编),以及机器码转化成汇编(反汇编),考研补充:指令格式、种类第三章计算机中数的表示、转换与运算8章节:3.1~3.6数据表示整数加减运算整数乘除运算浮点表示,加减运算整数加减算法分析、优化加法器设计乘除算法分析浮点数第四章处理器——数据通路与控制器的设计14章节:4.1~4.4单个组件设计MIPS指令系统ALU与ALU控制器单时钟数据通道多时钟数据通道控制器设计新版书只讲到单时钟,然后就流水线啦。流水还是留体系课。同时也为了配合实验,补充多时钟与控制器(FSM)内容。考研补充:总线型CPU设计,微指令控制第五章存贮体系结构8章节:5.1~5.5主要内容:存储器概论,位扩展字扩展Cache虚拟存储考研补充:存储器构成,位扩展、字扩展第六章接口处理器和外部设备8章节:6.1~6.6I/O概论磁盘系统总线系统、仲裁数据通讯:轮询、中断、DMA以概念为主复习225/1/274CourseObjectivesCourseObjectivesUnderstandmoderncomputers,theirevolution,andtrade-offsattheHW/SWinterfaceInstructionSetArchitectureComputerArithmeticPerformanceandMetricsPipeliningUnderstandthedesignofamoderncomputersystemDatapathdesignControldesignMemorySystemDesignI/OSystemDesign25/1/275WhatyouwillLearnWhatyouwillLearnHowareprogramswritteninhighlevellanguages(CorJava)translatedintothelanguageofthehardware,andhowdoeshardwareexecutether...