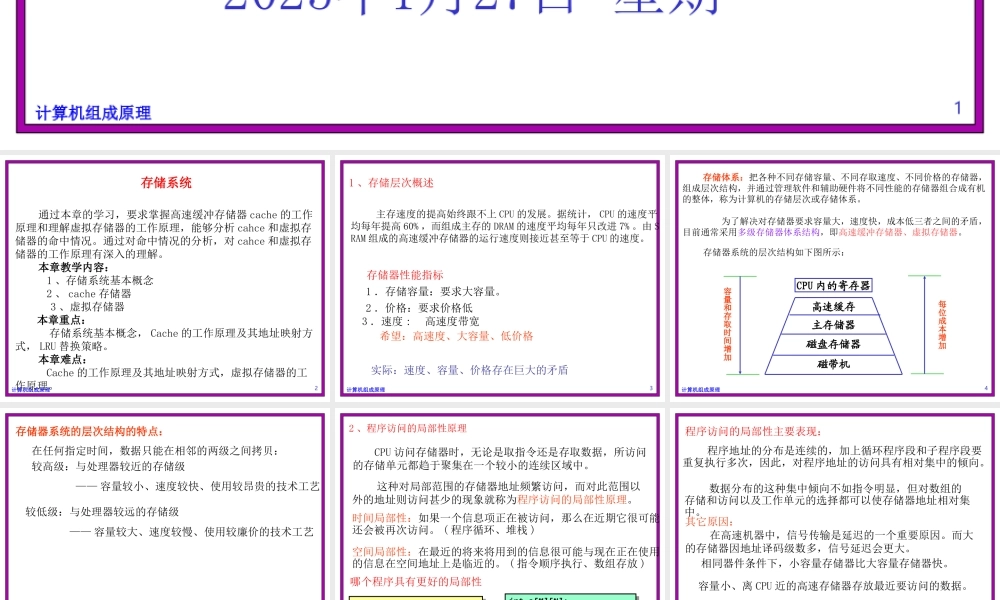

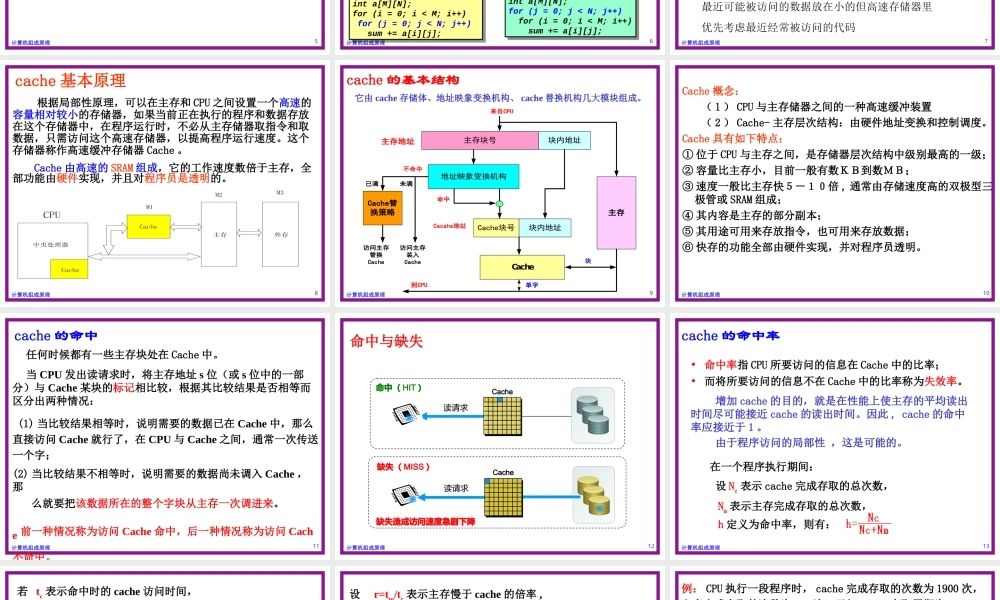

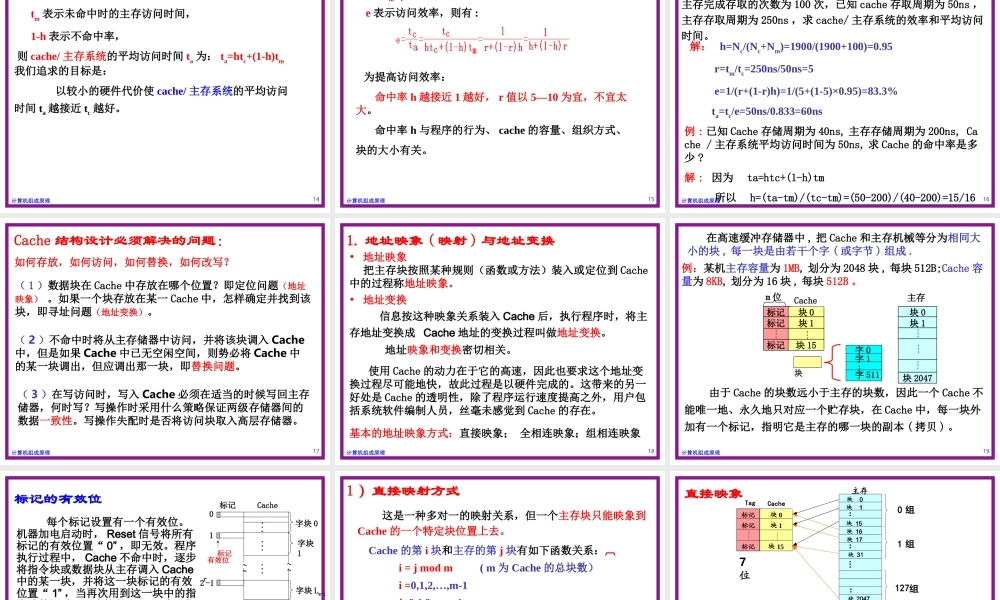

计算机组成原理1计算机组成原理计算机组成原理2025年1月27日星期一存储系统计算机组成原理2通过本章的学习,要求掌握高速缓冲存储器cache的工作原理和理解虚拟存储器的工作原理,能够分析cahce和虚拟存储器的命中情况。通过对命中情况的分析,对cahce和虚拟存储器的工作原理有深入的理解。本章教学内容:1、存储系统基本概念2、cache存储器3、虚拟存储器本章重点:存储系统基本概念,Cache的工作原理及其地址映射方式,LRU替换策略。本章难点:Cache的工作原理及其地址映射方式,虚拟存储器的工作原理。存储系统计算机组成原理31.存储容量:要求大容量。2.价格:要求价格低主存速度的提高始终跟不上CPU的发展。据统计,CPU的速度平均每年提高60%,而组成主存的DRAM的速度平均每年只改进7%。由SRAM组成的高速缓冲存储器的运行速度则接近甚至等于CPU的速度。1、存储层次概述存储器性能指标3.速度:高速度带宽实际:速度、容量、价格存在巨大的矛盾希望:高速度、大容量、低价格计算机组成原理4存储体系:把各种不同存储容量、不同存取速度、不同价格的存储器,组成层次结构,并通过管理软件和辅助硬件将不同性能的存储器组合成有机的整体,称为计算机的存储层次或存储体系。存储器系统的层次结构如下图所示:CPU内的寄存器高速缓存主存储器磁盘存储器磁带机容量和存取时间增加每位成本增加为了解决对存储器要求容量大,速度快,成本低三者之间的矛盾,目前通常采用多级存储器体系结构,即高速缓冲存储器、虚拟存储器。计算机组成原理5较低级:与处理器较远的存储级——容量较大、速度较慢、使用较廉价的技术工艺存储器系统的层次结构的特点:在任何指定时间,数据只能在相邻的两级之间拷贝:较高级:与处理器较近的存储级——容量较小、速度较快、使用较昂贵的技术工艺计算机组成原理62、程序访问的局部性原理CPU访问存储器时,无论是取指令还是存取数据,所访问的存储单元都趋于聚集在一个较小的连续区域中。时间局部性:如果一个信息项正在被访问,那么在近期它很可能还会被再次访问。(程序循环、堆栈)空间局部性:在最近的将来将用到的信息很可能与现在正在使用的信息在空间地址上是临近的。(指令顺序执行、数组存放)这种对局部范围的存储器地址频繁访问,而对此范围以外的地址则访问甚少的现象就称为程序访问的局部性原理。inta[M][N];for(i=0;i