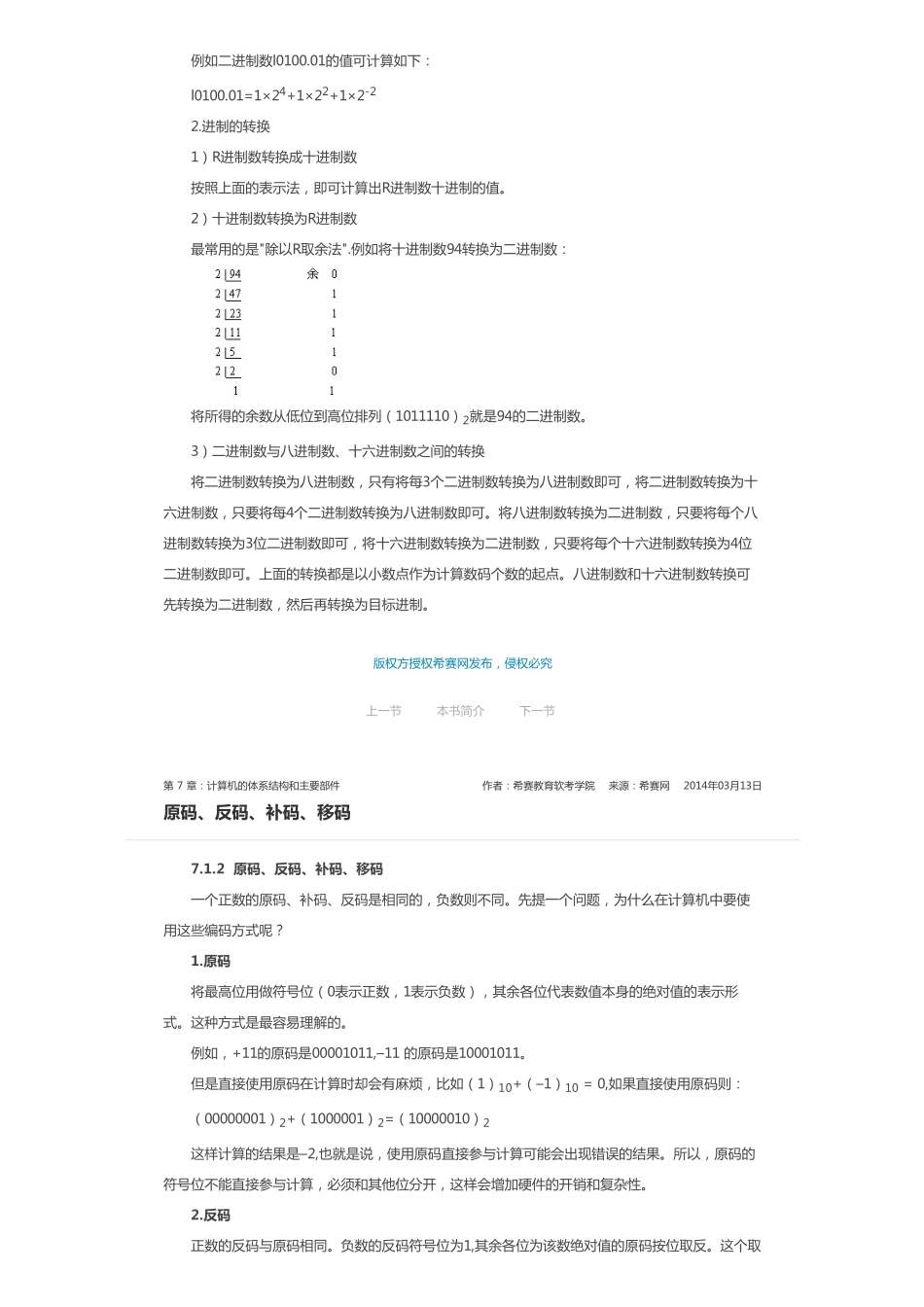

您现在的位置:希赛网>云阅读>软件设计师考试考点分析与真题详解(第4版)>机内代码及运算第7章:计算机的体系结构和主要部件作者:希赛教育软考学院来源:希赛网2014年01月26日机内代码及运算上一节本书简介下一节第7章:计算机的体系结构和主要部件作者:希赛教育软考学院来源:希赛网2014年03月13日数的进制第7章计算机的体系结构和主要部件也许有人认为系统设计师似乎不需要什么硬件的知识,计算机的硬件理论知识并非是空中楼阁,不是好看或者用来考试的,它是确确实实的每台计算机设计和制造的基础,而且在学习的过程中,我们能够发现许多在硬件上使用的原则在软件上使用同样有益。在很多时候,我们能发现,计算机软件和硬件并非截然分开,而是有个此消彼长、相互促进的发展过程。比如早期的中央处理器是没有浮点运算功能,浮点运算需要使用软件实现,而后来,许多处理器都内置了浮点运算功能。另外,嵌入式系统的软件设计师必须考虑硬件的问题。7.1机内代码及运算人人都知道计算机只处理二进制数据,二进制是最简单的进制方式,只有0和1两个基数,也就是说,计算机底层硬件只要能保持两个状态即可,这样使得计算机的底层设计变得简单,出错的概率也大为减小。当然二进制数据使得表示和保存数据的长度大大增加,但是大规模和超大规模的集成电路使得这成为次要的问题,人们能在越来越小的芯片空间里容纳越来越多的电路。另一方面计算机为了使得处理方便,其内部存储数据的格式和我们看见的是不同的。版权方授权希赛网发布,侵权必究7.1.1数的进制1.进制的表示法R进制,通常说法就是逢R进1.可以用的数为R个,分别是0,1,2,…,R–1.例如十进制数的基数为10,即可以用到的数码个数为10,它们是0,1,2,3,4,5,6,7,8,9.二进制数的基数为2,可用的数码个数为2,它们是0和1。为了把不同的进制数分开表示,避免造成混淆,采用下标的方式来表示一个数的进制,如十进制数56表示为:(56)10,八进制数42表示为:(42)8。对于任意一个R进制数,它的每一位数值等于该位的数码乘以该位的权数。权数由一个幂表示,即幂的底数是R,指数为k,k与该位和小数点之间的距离有关。当该位位于小数点左边,k值是该位和小数点之间数码的个数,而当该位位于小数点右边,k值是负值,其绝对值是该位和小数点之间数码的个数加1.例如十进制数1234.56,其数值可计算如下:1234.56=1×103+2×102+3×101+4×100+5×10-1+6×10-2上一节本书简介下一节第7章:计算机的体系结构和主要部件作...