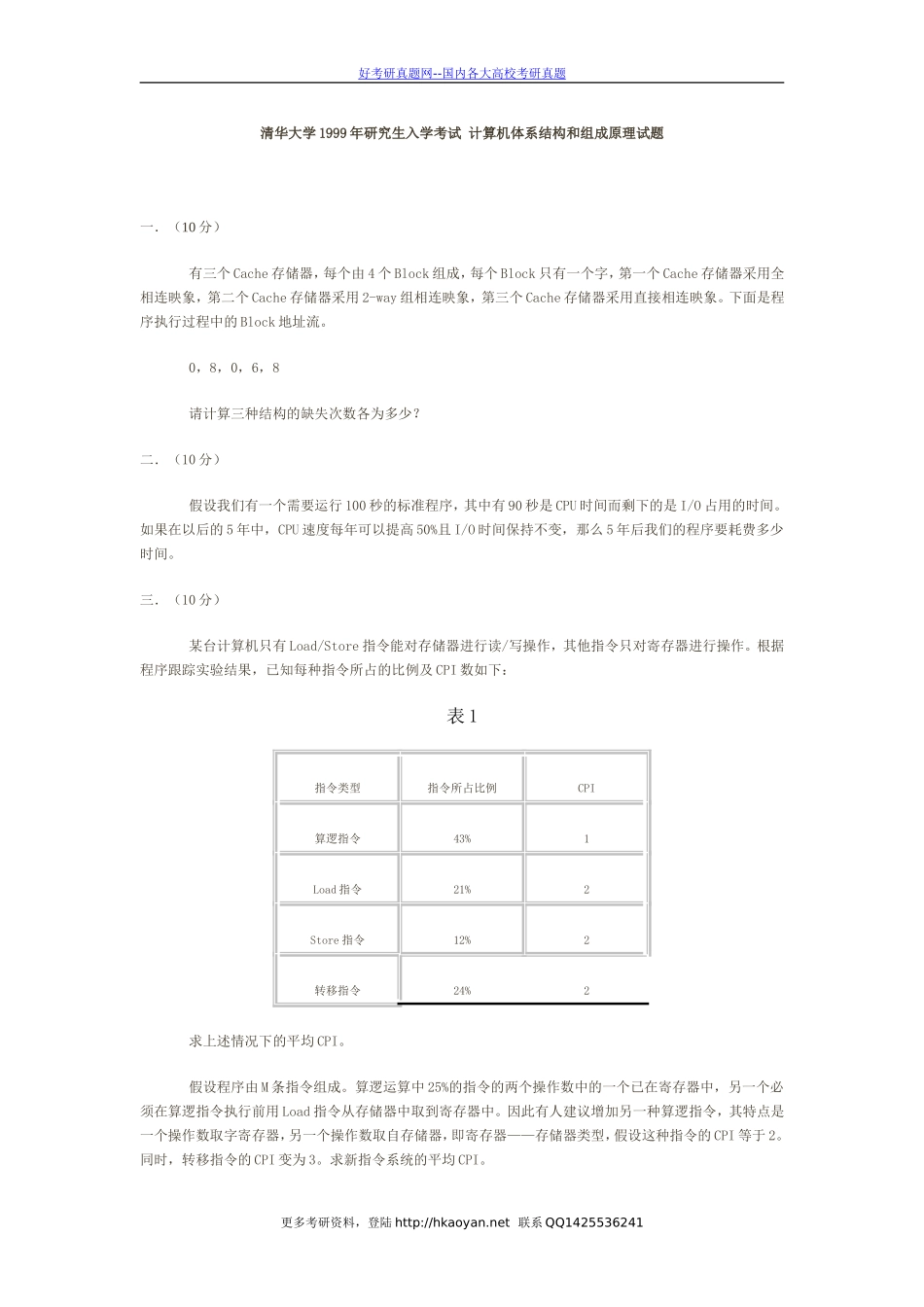

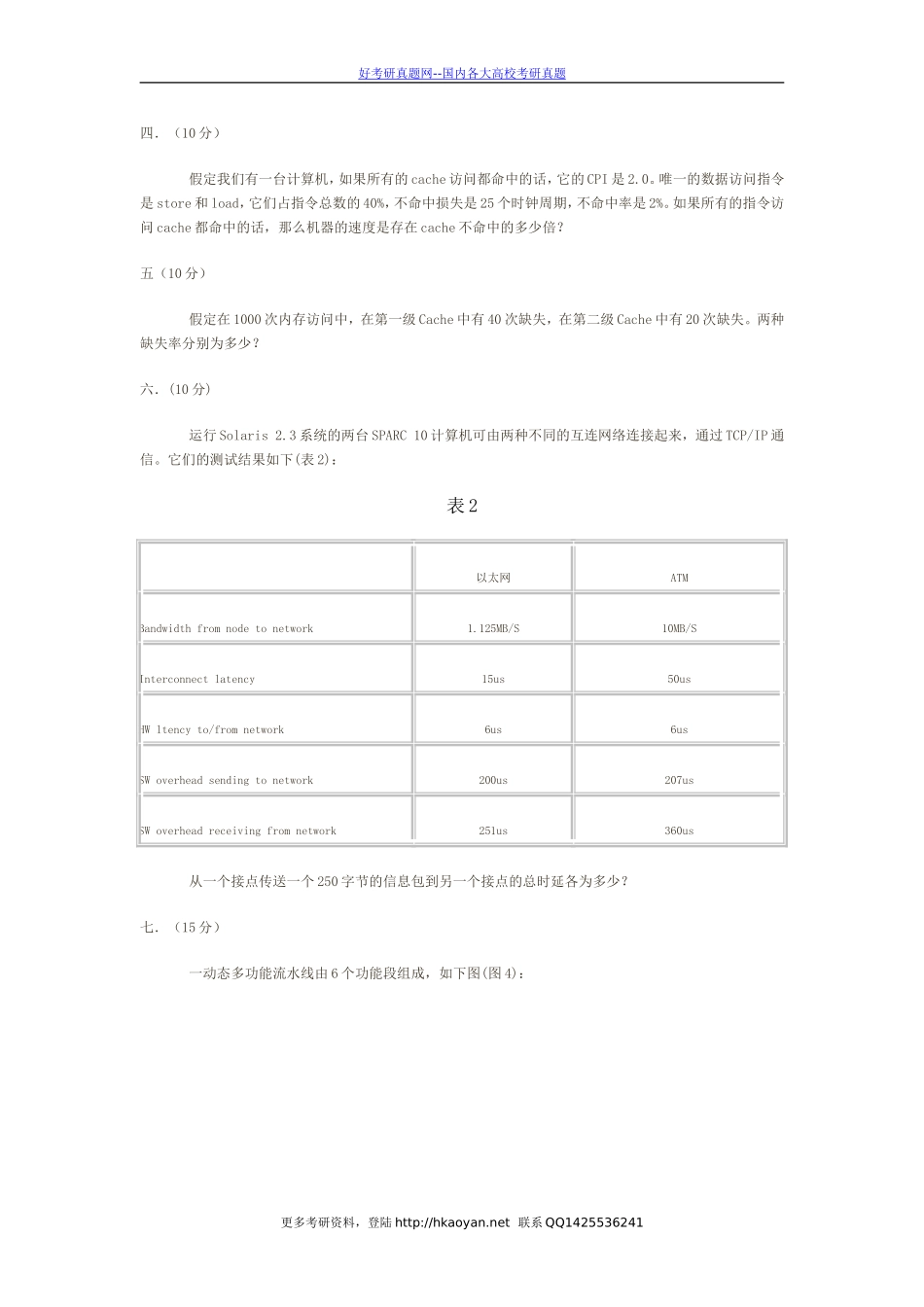

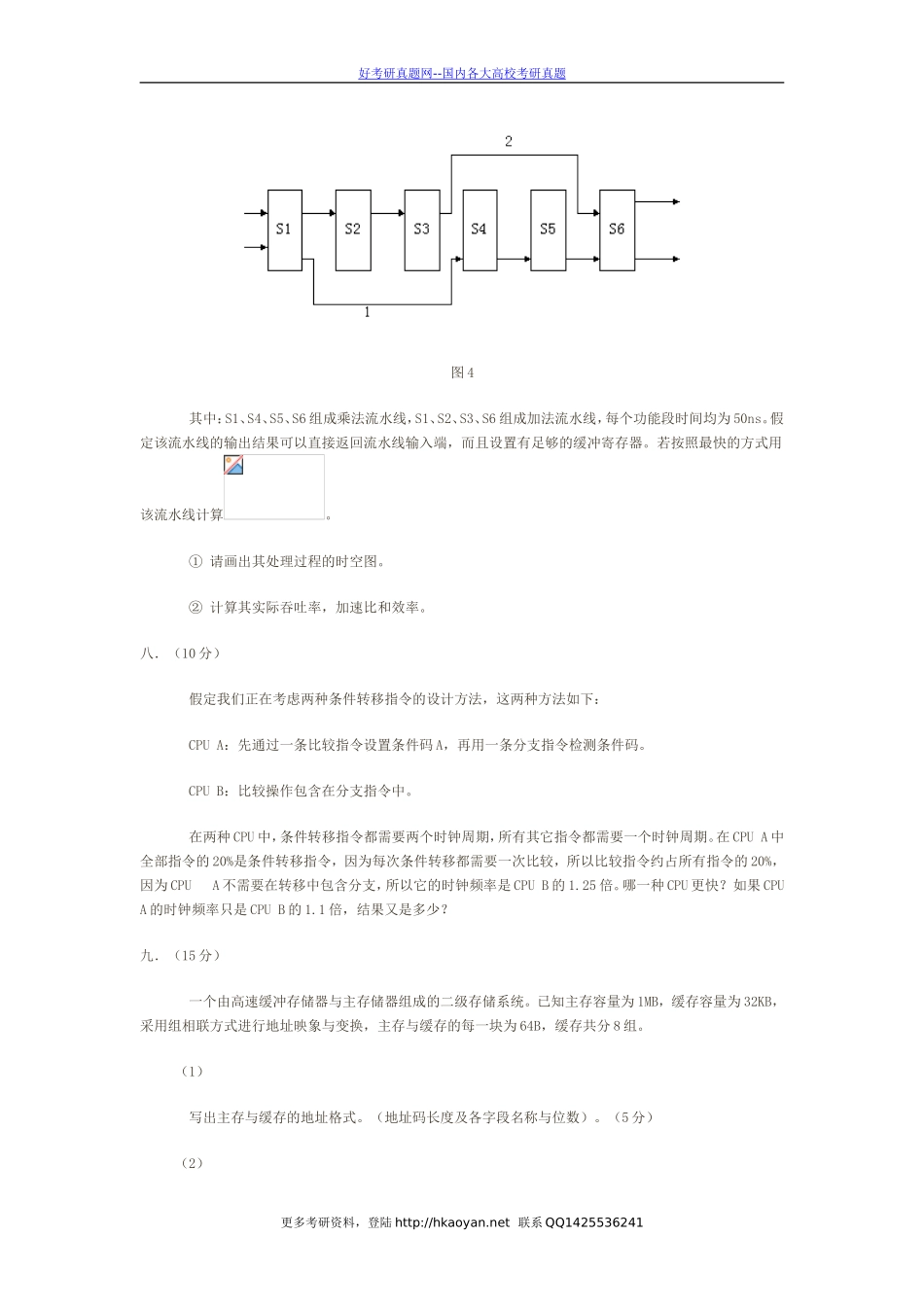

好考研真题网--国内各大高校考研真题清华大学1999年研究生入学考试计算机体系结构和组成原理试题一.(10分)有三个Cache存储器,每个由4个Block组成,每个Block只有一个字,第一个Cache存储器采用全相连映象,第二个Cache存储器采用2-way组相连映象,第三个Cache存储器采用直接相连映象。下面是程序执行过程中的Block地址流。0,8,0,6,8请计算三种结构的缺失次数各为多少?二.(10分)假设我们有一个需要运行100秒的标准程序,其中有90秒是CPU时间而剩下的是I/O占用的时间。如果在以后的5年中,CPU速度每年可以提高50%且I/O时间保持不变,那么5年后我们的程序要耗费多少时间。三.(10分)某台计算机只有Load/Store指令能对存储器进行读/写操作,其他指令只对寄存器进行操作。根据程序跟踪实验结果,已知每种指令所占的比例及CPI数如下:表1指令类型指令所占比例CPI算逻指令43%1Load指令21%2Store指令12%2转移指令24%2求上述情况下的平均CPI。假设程序由M条指令组成。算逻运算中25%的指令的两个操作数中的一个已在寄存器中,另一个必须在算逻指令执行前用Load指令从存储器中取到寄存器中。因此有人建议增加另一种算逻指令,其特点是一个操作数取字寄存器,另一个操作数取自存储器,即寄存器——存储器类型,假设这种指令的CPI等于2。同时,转移指令的CPI变为3。求新指令系统的平均CPI。更多考研资料,登陆http://hkaoyan.net联系QQ1425536241好考研真题网--国内各大高校考研真题四.(10分)假定我们有一台计算机,如果所有的cache访问都命中的话,它的CPI是2.0。唯一的数据访问指令是store和load,它们占指令总数的40%,不命中损失是25个时钟周期,不命中率是2%。如果所有的指令访问cache都命中的话,那么机器的速度是存在cache不命中的多少倍?五(10分)假定在1000次内存访问中,在第一级Cache中有40次缺失,在第二级Cache中有20次缺失。两种缺失率分别为多少?六.(10分)运行Solaris2.3系统的两台SPARC10计算机可由两种不同的互连网络连接起来,通过TCP/IP通信。它们的测试结果如下(表2):表2以太网ATMBandwidthfromnodetonetwork1.125MB/S10MB/SInterconnectlatency15us50usHWltencyto/fromnetwork6us6usSWoverheadsendingtonetwork200us207usSWoverheadreceivingfromnetwork251us360us从一个接点传送一个250字节的信息包到另一个接点的总时延各为多少?七.(15分)一动态多功能流水线由6个功能段组成,如下图(图4):更多考研资料,登陆...