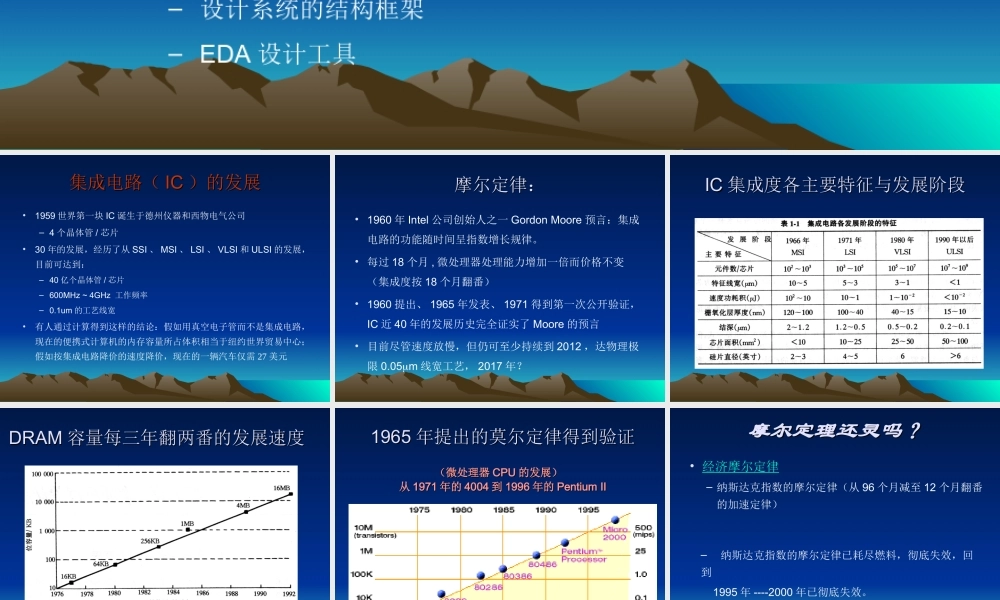

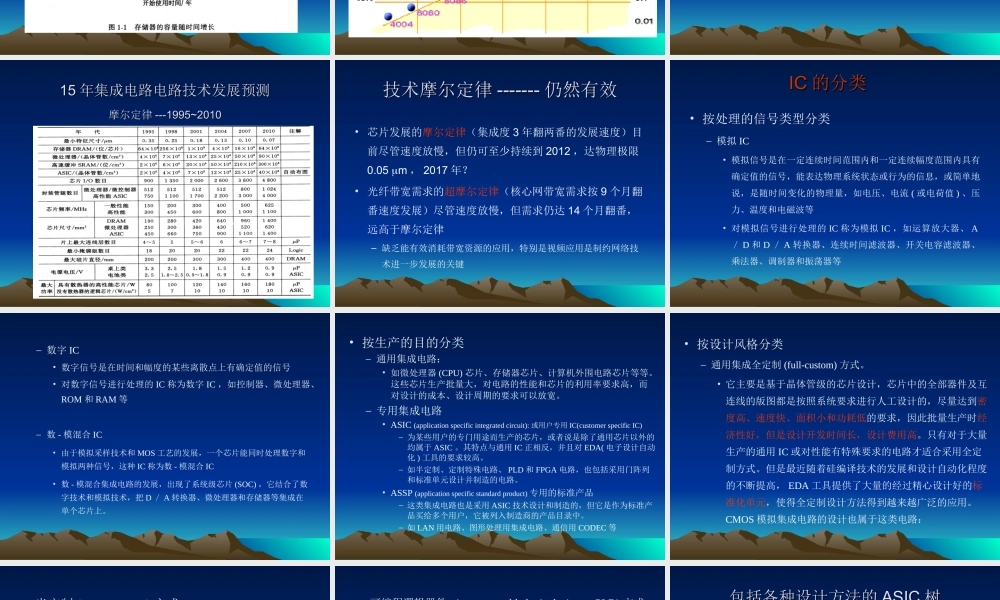

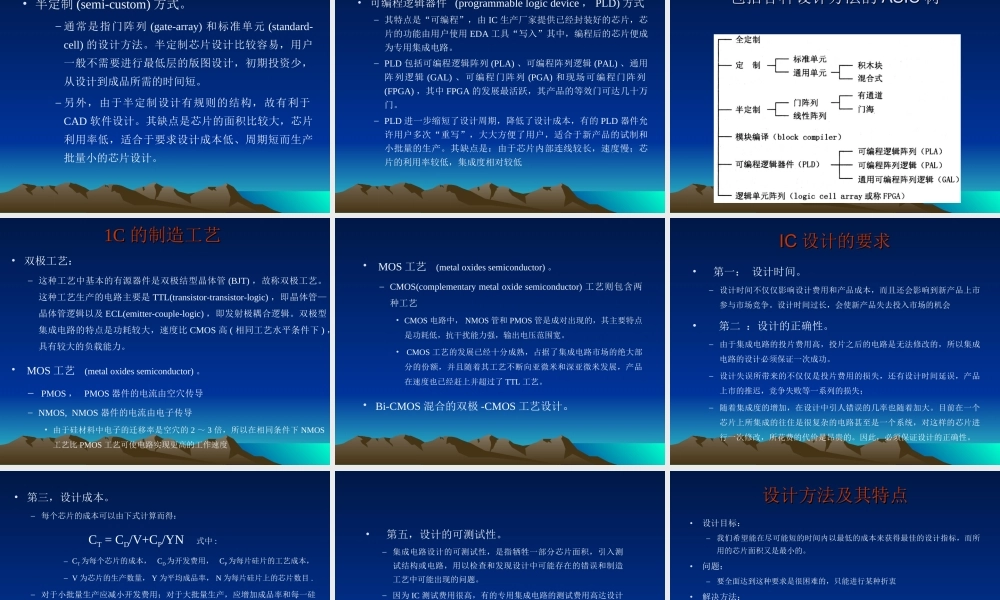

第一章集成电路设计概述第一章集成电路设计概述•集成电路(IC)的发展•IC的分类、制造工艺•IC设计的要求•设计方法及其特点•典型的设计流程–自顶向下–由底向上•集成电路设计方法和工具的变革–设计系统的结构框架–EDA设计工具•1959世界第一块IC诞生于德州仪器和西物电气公司–4个晶体管/芯片•30年的发展,经历了从SSI、MSI、LSI、VLSI和ULSI的发展,目前可达到:–40亿个晶体管/芯片–600MHz~4GHz工作频率–0.1um的工艺线宽•有人通过计算得到这样的结论:假如用真空电子管而不是集成电路,现在的便携式计算机的内存容量所占体积相当于纽约世界贸易中心;假如按集成电路降价的速度降价,现在的一辆汽车仅需27美元集成电路(集成电路(ICIC)的发展)的发展摩尔定律:摩尔定律:•1960年Intel公司创始人之一GordonMoore预言:集成电路的功能随时间呈指数增长规律。•每过18个月,微处理器处理能力增加一倍而价格不变(集成度按18个月翻番)•1960提出、1965年发表、1971得到第一次公开验证,IC近40年的发展历史完全证实了Moore的预言•目前尽管速度放慢,但仍可至少持续到2012,达物理极限0.05m线宽工艺,2017年?ICIC集成度各主要特征与发展阶段集成度各主要特征与发展阶段DRAMDRAM容量每三年翻两番的发展速度容量每三年翻两番的发展速度19651965年提出的莫尔定律得到验证年提出的莫尔定律得到验证(微处理器(微处理器CPUCPU的发展)的发展)从从19711971年的年的40044004到到19961996年的年的PentiumIIPentiumII摩尔定理还灵吗?摩尔定理还灵吗?•经济摩尔定律–纳斯达克指数的摩尔定律(从96个月减至12个月翻番的加速定律)–纳斯达克指数的摩尔定律已耗尽燃料,彻底失效,回到1995年----2000年已彻底失效。1515年集成电路电路技术发展预测年集成电路电路技术发展预测摩尔定律摩尔定律---1995~2010---1995~2010技术摩尔定律技术摩尔定律--------------仍然有效仍然有效•芯片发展的摩尔定律(集成度3年翻两番的发展速度)目前尽管速度放慢,但仍可至少持续到2012,达物理极限0.05m,2017年?•光纤带宽需求的超摩尔定律(核心网带宽需求按9个月翻番速度发展)尽管速度放慢,但需求仍达14个月翻番,远高于摩尔定律–缺乏能有效消耗带宽资源的应用,特别是视频应用是制约网络技术进一步发展的关键ICIC的分类的分类•按处理的信号类型分类–模拟IC•模拟信号是在一定连续时间范围内和一定连续幅度范围内具有确定值的信号,能表达物理...