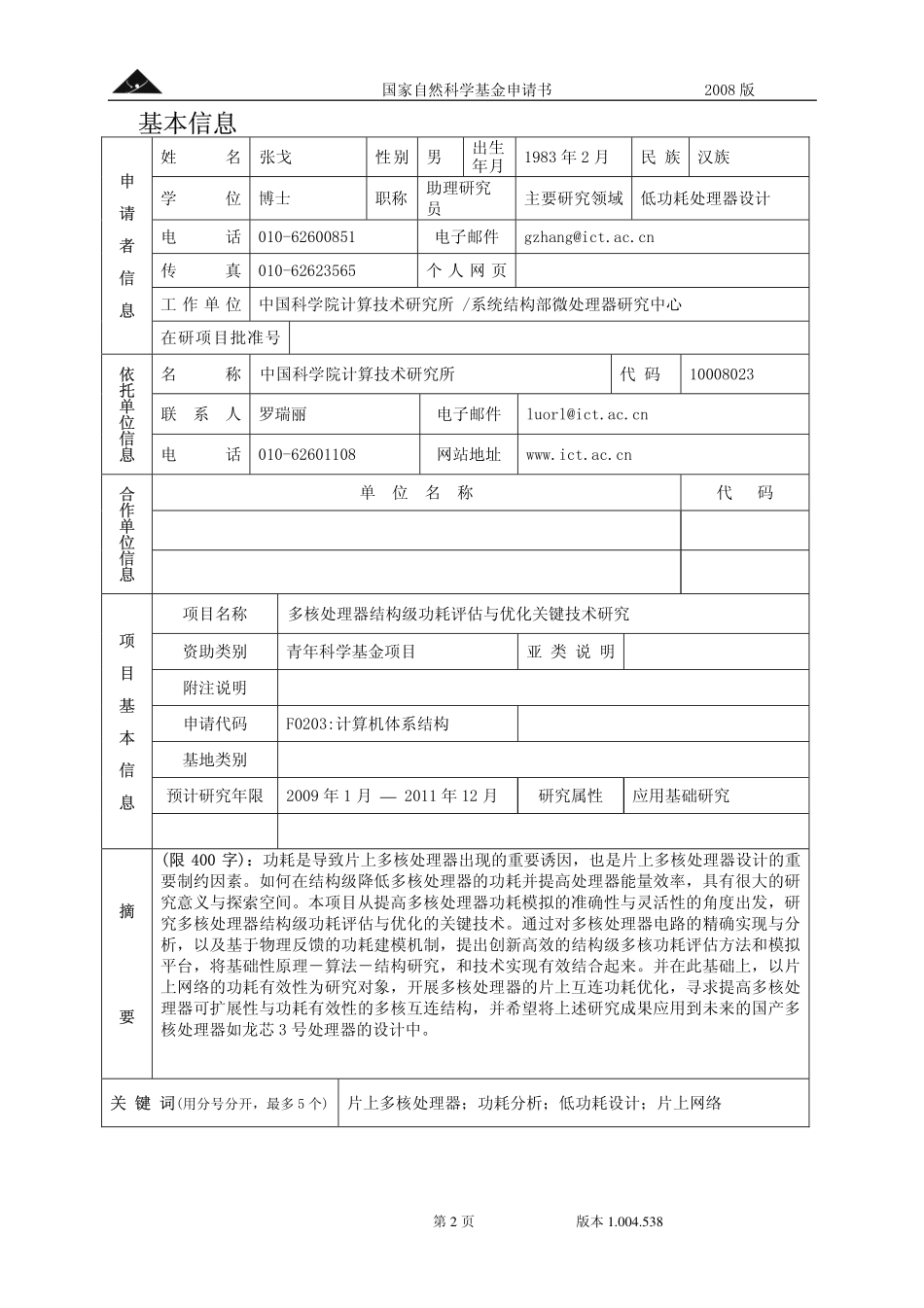

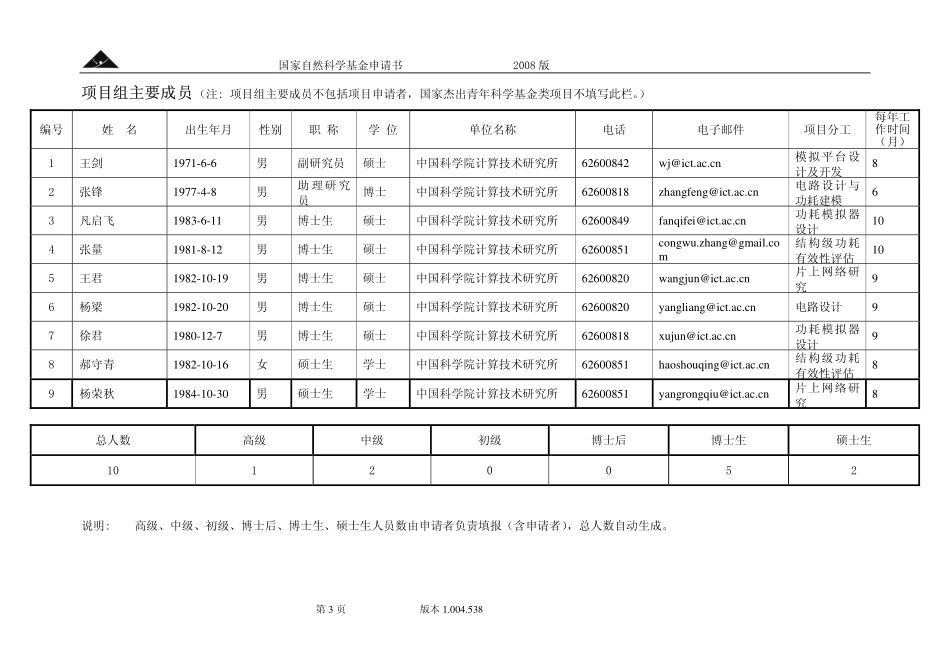

申请代码:受理部门:收件日期:受理编号:国家自然科学基金申请书(2008版)资助类别:亚类说明:附注说明:项目名称:申请者:电话:依托单位:通讯地址:邮政编码:单位电话:电子邮件:申报日期:2008年3月15日国家自然科学基金委员会您现在不能检查保护文档或打印文档,请根据以下三个步骤操作:1)如果您是Word2000或以上版本用户,请把Word宏的安全性设为:"中"方法:Word菜单->工具->宏->安全性->安全级,设置为"中"(如果您是Word97用户,继续执行以下步骤)2)关闭本文档,重新打开本文档3)点击"启用宏"按钮,即可开始填写本文档或打印了国家自然科学基金申请书2008版第2页版本1.004.538基本信息pRomYhas姓名张张戈性别男出生年月1983年2月民族汉族学位博士职称助理研究员主要研究领域低功耗处理器设计电话010-62600851电子邮件gzhang@ict.ac.cn传真010-62623565个人网页工作单位中国科学院计算技术研究所/系统结构部微处理器研究中心申请者信息在研项目批准号名称中国科学院计算技术研究所代码10008023联系人罗瑞丽电子邮件luorl@ict.ac.cn依托单位信息电话010-62601108网站地址www.ict.ac.cn单位名称代码合作单位信息项目名称多核处理器结构级功耗评估与优化关键技术研究资助类别青年科学基金项目亚类说明附注说明申请代码F0203:计算机体系结构基地类别预计研究年限2009年1月—2011年12月研究属性应用基础研究项目基本信息摘要(限400字):功耗是导致片上多核处理器出现的重要诱因,也是片上多核处理器设计的重要制约因素。如何在结构级降低多核处理器的功耗并提高处理器能量效率,具有很大的研究意义与探索空间。本项目从提高多核处理器功耗模拟的准确性与灵活性的角度出发,研究多核处理器结构级功耗评估与优化的关键技术。通过对多核处理器电路的精确实现与分析,以及基于物理反馈的功耗建模机制,提出创新高效的结构级多核功耗评估方法和模拟平台,将基础性原理-算法-结构研究,和技术实现有效结合起来。并在此基础上,以片上网络的功耗有效性为研究对象,开展多核处理器的片上互连功耗优化,寻求提高多核处理器可扩展性与功耗有效性的多核互连结构,并希望将上述研究成果应用到未来的国产多核处理器如龙芯3号处理器的设计中。关键词(用分号分开,最多5个)片上多核处理器;功耗分析;低功耗设计;片上网络国家自然科学基金申请书2008版第3页版本1.004.538项目组主要成员(注:项目组主要成员不包括项目申请者,国家杰出青年科学基金类项目不...