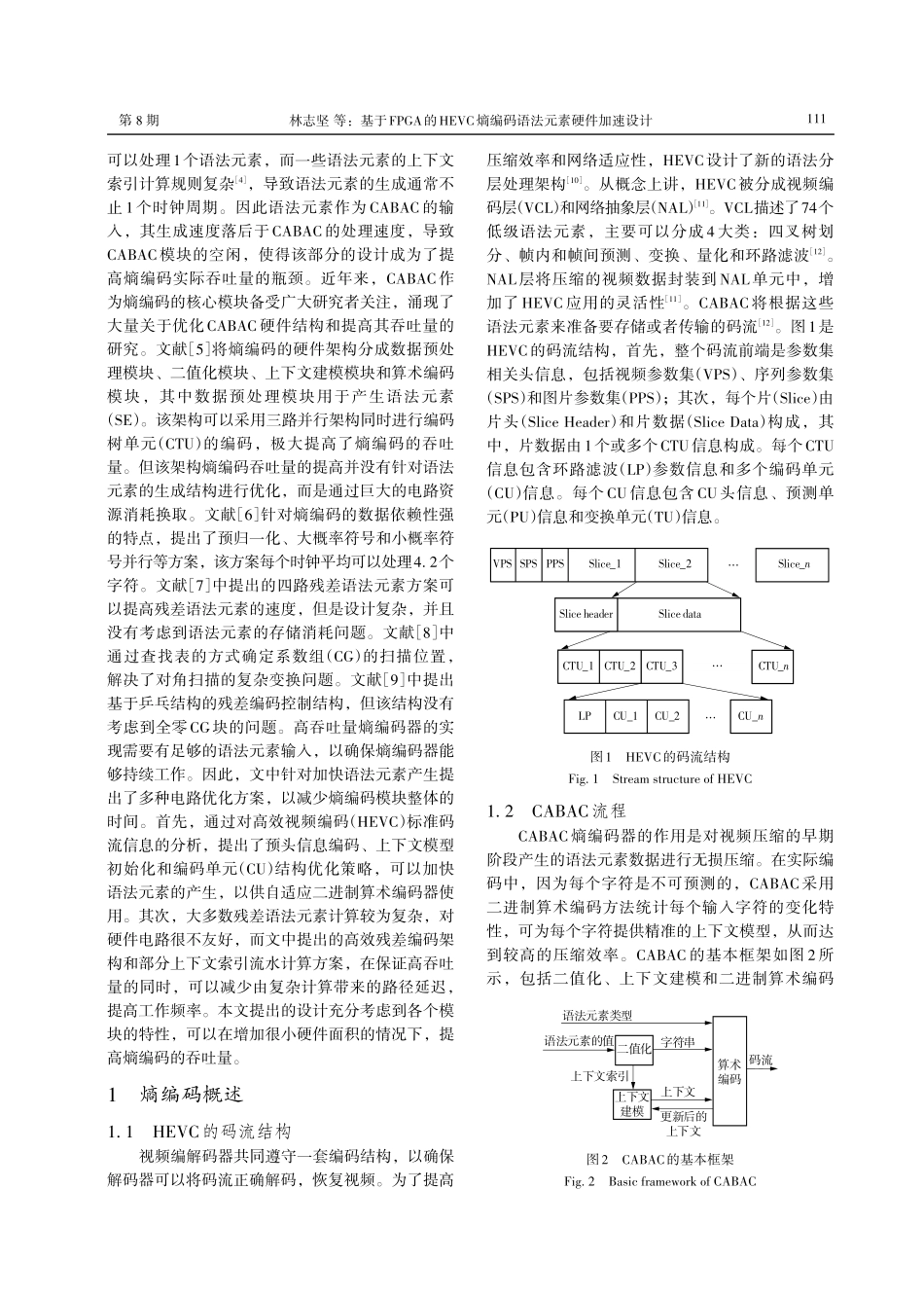

第51卷第8期2023年8月Vol.51No.8August2023华南理工大学学报(自然科学版)JournalofSouthChinaUniversityofTechnology(NaturalScienceEdition)基于FPGA的HEVC熵编码语法元素硬件加速设计林志坚黄萍郑明魁†陈平平(福州大学物理与信息工程学院,福建福州350108)摘要:高效视频编码标准(HEVC/H.265)是目前国际市场上广泛采用的视频编码标准。基于上下文自适应二进制算术编码(CABAC)作为HEVC熵编码的核心编码方式,通过建立更加精准的概率模型,提高了算术编码的压缩效率。此外,HEVC定义了更多种类的语法元素并建立更复杂的编码结构,进一步减少信息冗余,从而降低了码率。然而,语法元素作为CABAC的输入,其预处理过程的高复杂性,增加了硬件并行难度,导致熵编码硬件的吞吐率难以提高,成为HEVC编码器实现更高分辨率实时编码的瓶颈之一。为了进一步加快熵编码模块的速度,本文设计了一种基于现场可编程门阵列(FPGA)的高吞吐量CABAC熵编码架构。该架构提出的预头信息编码、上下文模型初始化和编码单元(CU)结构优化策略,可以加快语法元素的产生,以供自适应二进制算术编码器使用;通过高效的残差编码架构和部分上下文索引流水计算方案,在保持高吞吐量的同时,可以减少由复杂计算带来的路径延迟,提高工作频率。本设计使用90nm标准单元库进行综合,共使用了2.099×104个逻辑门数,工作频率可以达到200MHz。本文对HEVC官方提供的视频序列进行仿真测试,统计了在不同量化参数(QP)下编码1个编码树单元(CTU)所需要的时间,实验统计数据表明,本文设计使得编码1个CTU的时间平均节省了38.2%。关键词:熵编码;CABAC;FPGA;吞吐率;语法元素中图分类号:TP391.4文章编号:1000-565X(2023)08-0110-08随着智能手机和短视频的普及,视频在全网数据流量占比已接近70%。2013年,为了满足人们对视频更高质量的要求,国际电联(ITU)正式批准通过了高效视频编码(HEVC/H.265)标准,该标准较高级视频编码(AVC/H.264)标准的编码效率大约提高50%[1]。编码效率的提升,降低了对视频传输和存储的带宽要求[2],因此HEVC可以支持4k和8k的分辨率[3]。熵编码是HEVC的最后一个环节,可以很大程度压缩视频的熵冗余。相较于AVC/H.264,HEVC保留了唯一的熵编码方式——上下文自适应二进制算术编码(CABAC),用于编码片数据(Slicedata)。虽然CABAC具有编码效率的优势,但其复杂度也成倍增加[4]。目前,普遍的CABAC硬件设计1个时钟周期doi:10....