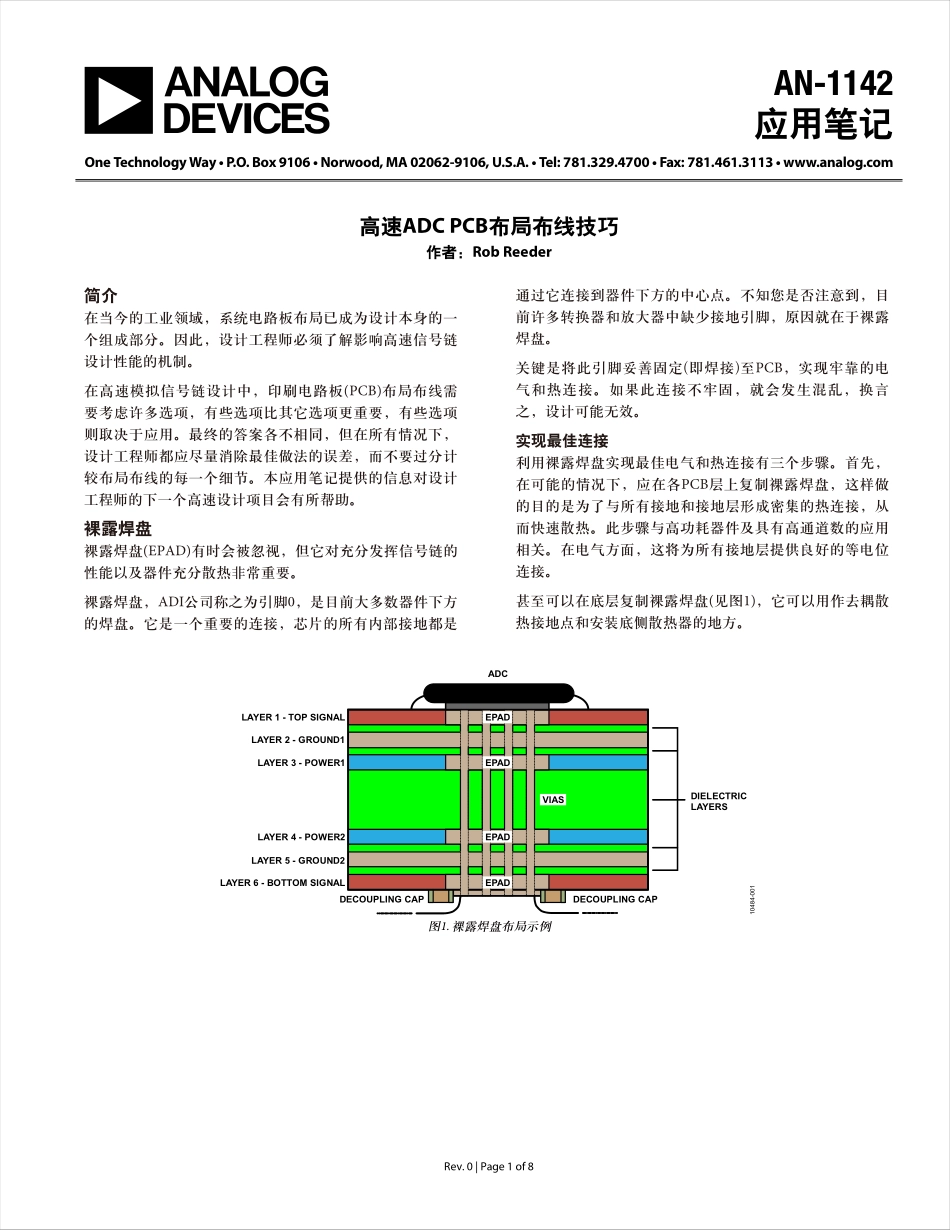

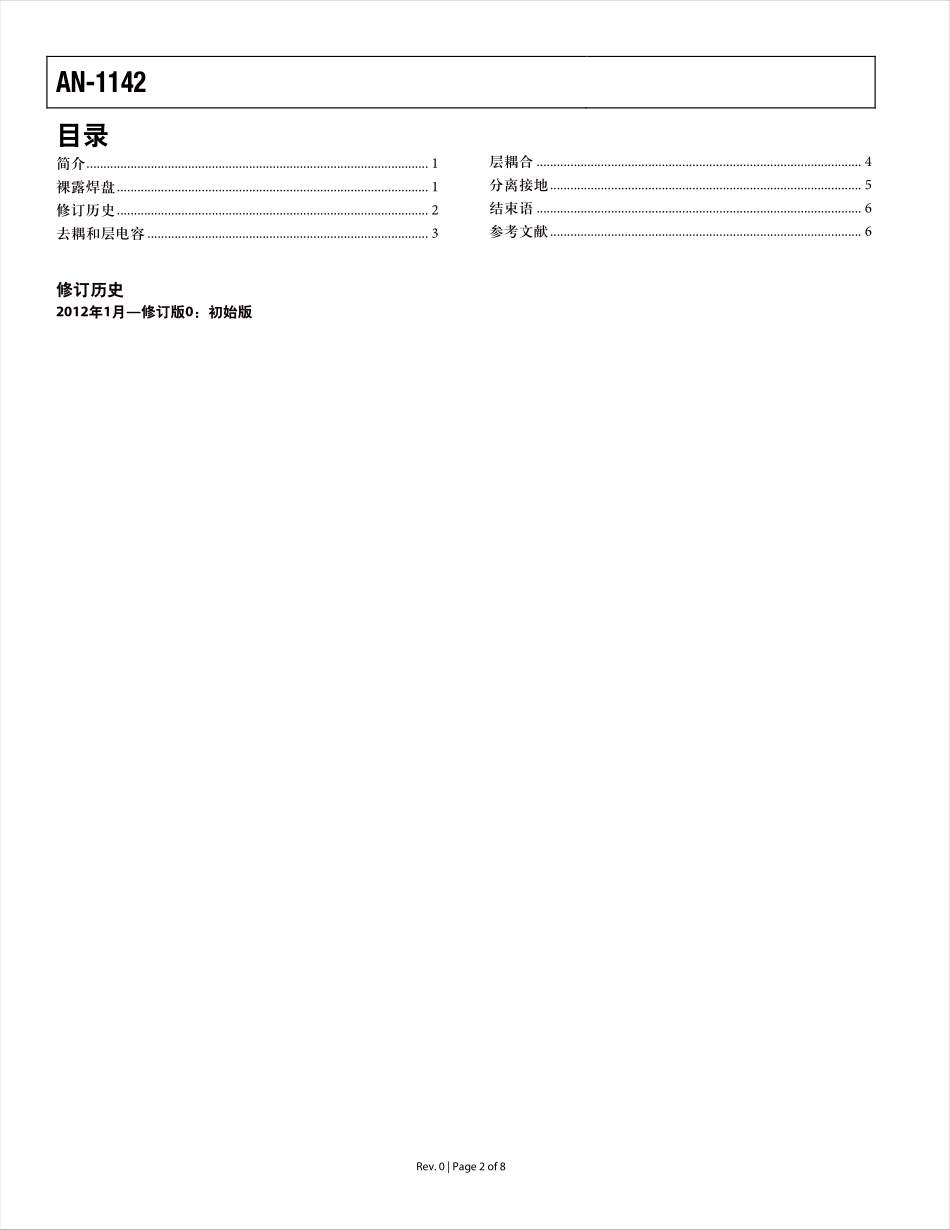

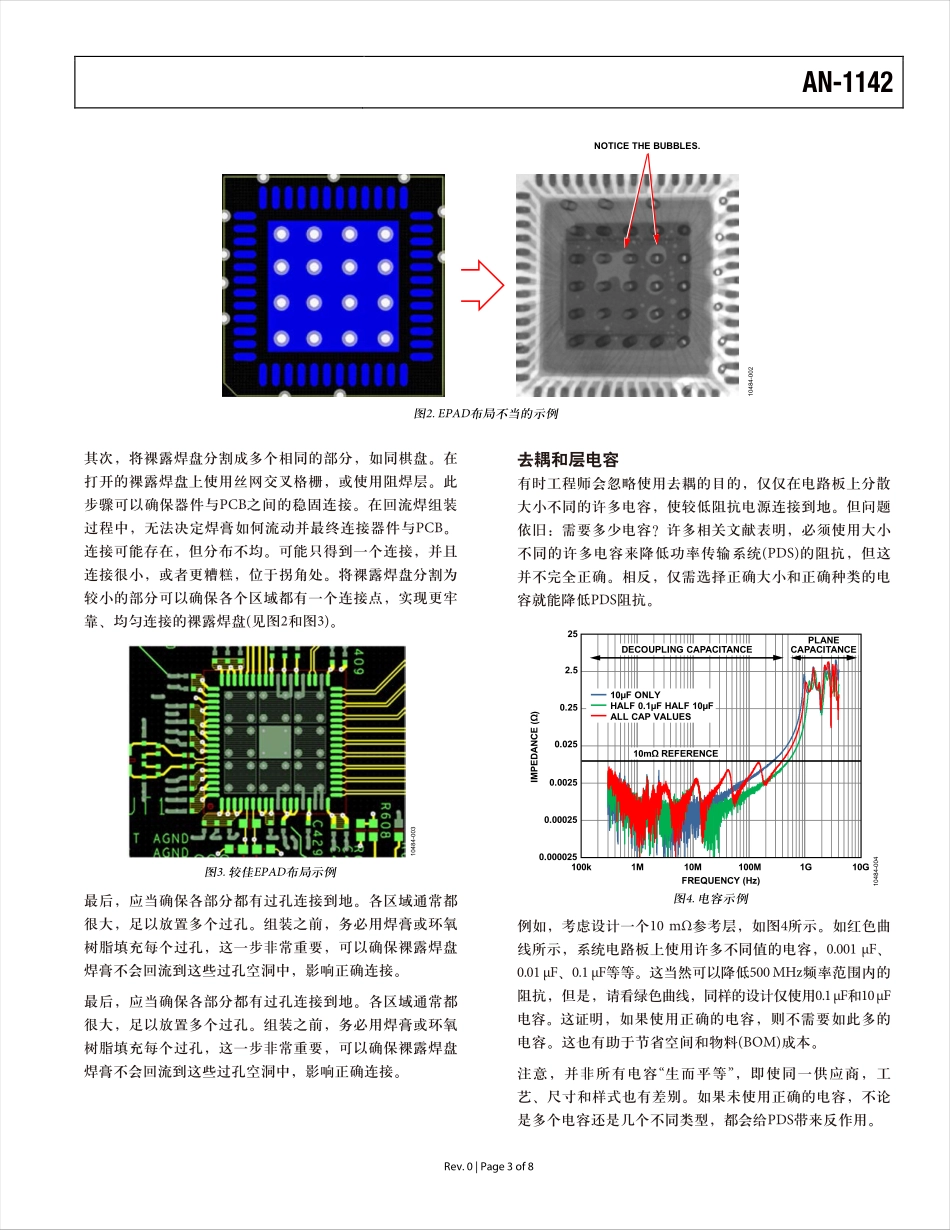

应用笔记AN-1142OneTechnologyWay•P.O.Box9106•Norwood,MA02062-9106,U.S.A.•Tel:781.329.4700•Fax:781.461.3113•www.analog.com高速ADCPCB布局布线技巧作者:RobReederRev.0|Page1of8ADCDECOUPLINGCAP10484-001DECOUPLINGCAPLAYER1-TOPSIGNALLAYER2-GROUND1LAYER3-POWER1LAYER5-GROUND2LAYER6-BOTTOMSIGNALLAYER4-POWER2DIELECTRICLAYERSEPADEPADEPADEPADVIAS简介在当今的工业领域,系统电路板布局已成为设计本身的一个组成部分。因此,设计工程师必须了解影响高速信号链设计性能的机制。在高速模拟信号链设计中,印刷电路板(PCB)布局布线需要考虑许多选项,有些选项比其它选项更重要,有些选项则取决于应用。最终的答案各不相同,但在所有情况下,设计工程师都应尽量消除最佳做法的误差,而不要过分计较布局布线的每一个细节。本应用笔记提供的信息对设计工程师的下一个高速设计项目会有所帮助。裸露焊盘裸露焊盘(EPAD)有时会被忽视,但它对充分发挥信号链的性能以及器件充分散热非常重要。裸露焊盘,ADI公司称之为引脚0,是目前大多数器件下方的焊盘。它是一个重要的连接,芯片的所有内部接地都是通过它连接到器件下方的中心点。不知您是否注意到,目前许多转换器和放大器中缺少接地引脚,原因就在于裸露焊盘。关键是将此引脚妥善固定(即焊接)至PCB,实现牢靠的电气和热连接。如果此连接不牢固,就会发生混乱,换言之,设计可能无效。实现最佳连接利用裸露焊盘实现最佳电气和热连接有三个步骤。首先,在可能的情况下,应在各PCB层上复制裸露焊盘,这样做的目的是为了与所有接地和接地层形成密集的热连接,从而快速散热。此步骤与高功耗器件及具有高通道数的应用相关。在电气方面,这将为所有接地层提供良好的等电位连接。甚至可以在底层复制裸露焊盘(见图1),它可以用作去耦散热接地点和安装底侧散热器的地方。图1.裸露焊盘布局示例Rev.0|Page2of8目录AN-1142简介.....................................................................................................1裸露焊盘............................................................................................1修订历史............................................................................................2去耦和层电容...................................................................................3层耦合........................................