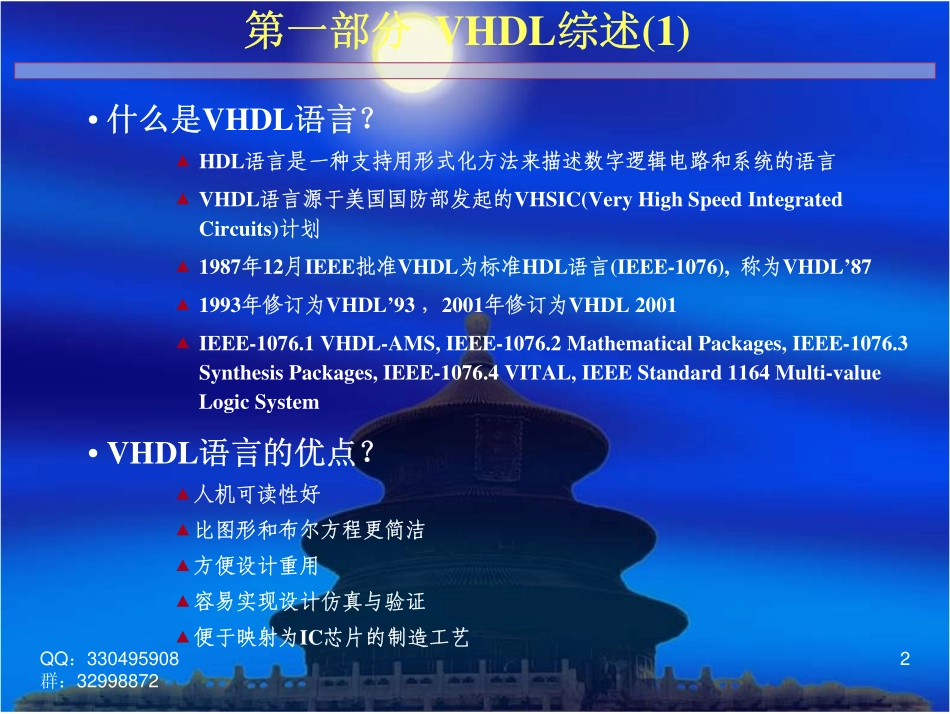

QQ:330495908群:329988721VHDLVHDLVHDLANDITSANDITSANDITSAAAPPLICATIONSPPLICATIONSPPLICATIONS缪善林QQ:330495908群:32998872哈尔滨工程大学信息与通信工程学院VHDL语言及其应用QQ:330495908群:329988722第一部分VHDL综述(1)•什么是VHDL语言?▲HDL语言是一种支持用形式化方法来描述数字逻辑电路和系统的语言▲VHDL语言源于美国国防部发起的VHSIC(VeryHighSpeedIntegratedCircuits)计划▲1987年12月IEEE批准VHDL为标准HDL语言(IEEE-1076),称为VHDL’87▲1993年修订为VHDL’93,2001年修订为VHDL2001▲IEEE-1076.1VHDL-AMS,IEEE-1076.2MathematicalPackages,IEEE-1076.3SynthesisPackages,IEEE-1076.4VITAL,IEEEStandard1164Multi-valueLogicSystem•VHDL语言的优点?▲人机可读性好▲比图形和布尔方程更简洁▲方便设计重用▲容易实现设计仿真与验证▲便于映射为IC芯片的制造工艺QQ:330495908群:329988723第一部分VHDL综述(2)•自顶向下设计▲VHDL语言支持自顶向下的系统划分,直至划分后的最底层单元能用图元(primitiveelement)来实现为止▲图元就是基本逻辑单元、宏模型或IP_core•VHDL的基本模型▲行为模型:用于描述数字器件或系统的功能,统指数学方程表示的模型▲时序模型:用于描述数字器件或系统的激励与响应间的关系,统指布尔方程表示的模型▲结构模型:用于描述自顶向下划分系统形成的各个基本单元间的互连关系,统指用元件互连生成的电路模型QQ:330495908群:329988724第一部分VHDL综述(3)•VHDL的基本设计流程QQ:330495908群:329988725第一部分VHDL综述(4)•VHDL的主要应用领域▲智能模块(IP)的研发IP:用VHDL语言编写,经逻辑优化和功能验证的可生成VLSI中各种功能单元的软件群,例如,无线通信产品、网上设备、中央处理器(通用CPU)、DSP、PCI、USB、嵌入式CPU▲单芯片全功能集成系统设计:SoPC系统、嵌入式计算、ASIC验证▲功能可重置系统的设计:远程系统升级、可重配置设计•FPGA的发展方向▲多用途:CAM,RAM、PLL▲高密度、低功耗、低成本:MAXII系列、CycloneII系列▲嵌入硬核、超高速:Stratix系列、StratixII系列、StratixGX系列▲超低成本:结构化的ASICs,例如,HardCopy系列▲嵌入CPU软核:Nios、NiosIIQQ:330495908群:329988726第一部分VHDL综述(5)•Altera公司的最新FPGA芯片QQ:330495908群:329988727第二部分VHDL语言的学习基础(1)•书写规定与基本句法单元▲书写规定保留字用黑体小写字母表示类型字用...