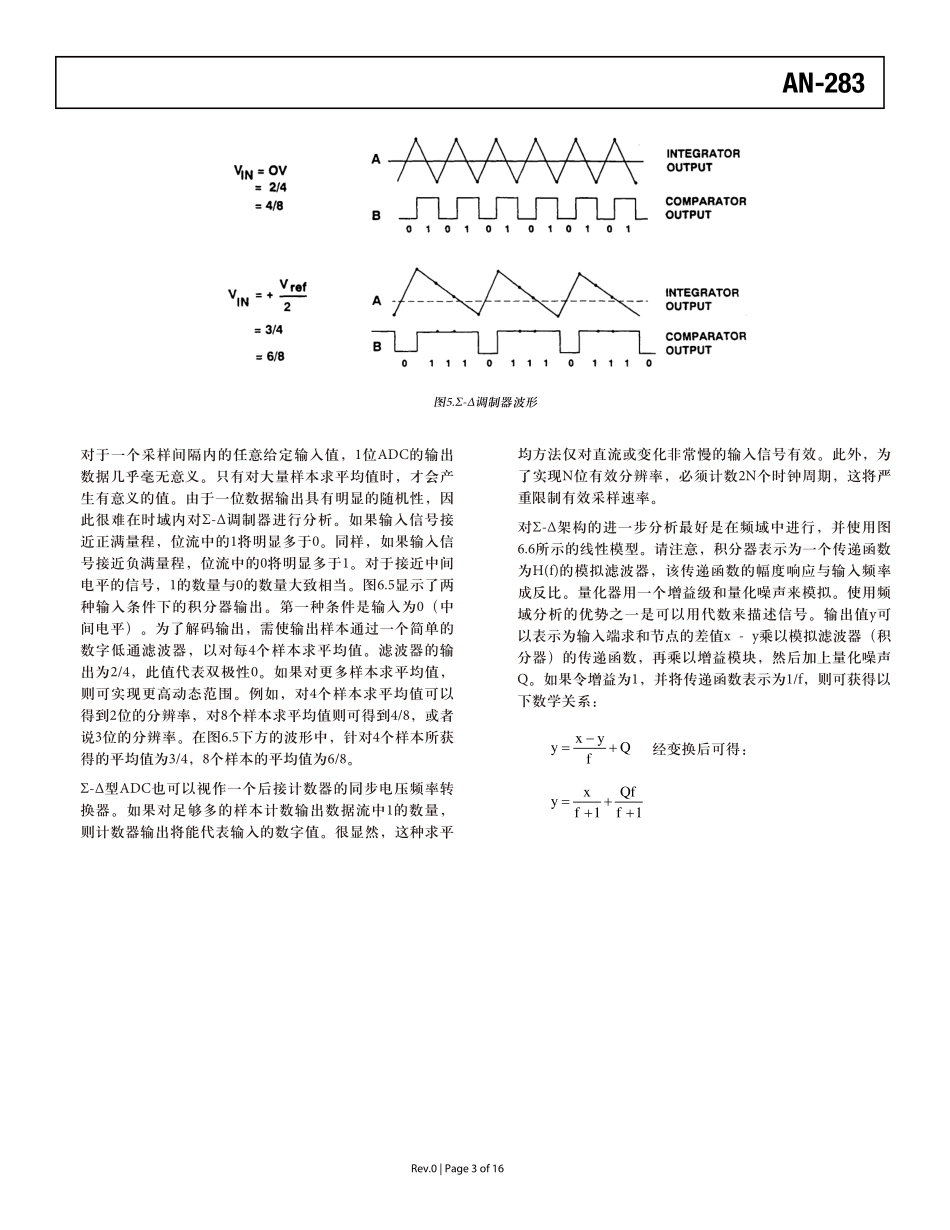

应用笔记Σ-Δ转换器工作原理涉及到的关键概念包括过采样、噪声整形(使用Σ-Δ调制器)、数字滤波和抽取。过采样过采样概念已在前文第三部分中讨论过,下面的图6.2和图6.3再次阐释了这一概念。正如前文所述,过采样的一个重要好处是降低了对模拟抗混叠滤波器的滚降要求。数字滤波器将fS/2和kffS/2之间的量化噪声(在奈奎斯特带宽范围,其均方根值为q/,其中q为LSB的权重)从输出中消除(k为过采样比),其结果是总信噪比提高了相当于10log10(k)的量。不过,对于所获得的额外分辨率而言,这一代价太高:为使信噪比提高区区6dB(1位),就要求过采样比达到4。为使过采样比保持在合理范围内,可以对量化噪声的频谱进行整形,使得绝大部分噪声落在fS/2与kfS/2之间,只有一小部分留在DC与fS/2之间。这正是Σ-Δ调制器在Σ-Δ型ADC中所起到的作用。噪声谱经过调制器的整形之后,数字滤波器就可以消除大部分量化噪声能量,从而大幅提高总信噪比(以及相应的动态范围)。Σ-Δ概述过去几年间,Σ-Δ架构由于在混合信号VLSI工艺中有助于实现高分辨率ADC,因而日益受到青睐。然而,直到最近,商业化生产这些器件所需的工艺技术尚未问世。现在,1微米及更小的CMOS几何结构的制造条件已经成熟,因此Σ-Δ转换器在某些类型的应用中将变得更为常见,特别是在单芯片上集成ADC、DAC和DSP功能的混合信号IC中,Σ-Δ转换器的使用将尤为普遍。从概念上讲,Σ-Δ转换器的数字特性多于模拟特性,但这并未降低Σ-Δ型ADC的模拟部分的重要性。五阶Σ-Δ调制器的设计(例如在双通道18位ADCAD1879中)绝不是轻而易举的小事一桩,数字滤波器同样如此。Σ-Δ转换器本质上是一种过采样转换器,尽管过采样只是成就整体性能的多种技术中的一种。总的说来,Σ-Δ转换器是利用分辨率非常低(1位)的ADC以极高采样速率对模拟信号进行数字化处理。但通过将过采样技术与噪声整形和数字滤波技术结合使用,使有效分辨率得以提高。然后,通过抽取过程降低ADC输出端的有效采样速率。1位量化器和DAC的线性度使Σ-Δ型ADC表现出极佳的微分和积分线性度,并且不必像其它ADC架构那样需要调整。Σ-Δ型ADC和DACRev.0|Page1of16AN-283■混合信号VLSI芯片的理想拓扑结构■过采样■利用Σ-Δ调制器进行噪声谱整形■数字滤波■抽取■可实现16位及更高的分辨率图1.Σ-Δ概念图2.采用模拟低通滤波器进行奈奎斯特频率采样12采用模拟低通滤波器进行奈奎斯特频率采样Rev.0|Page2of16图3.采用模拟和数字滤波进行过采...