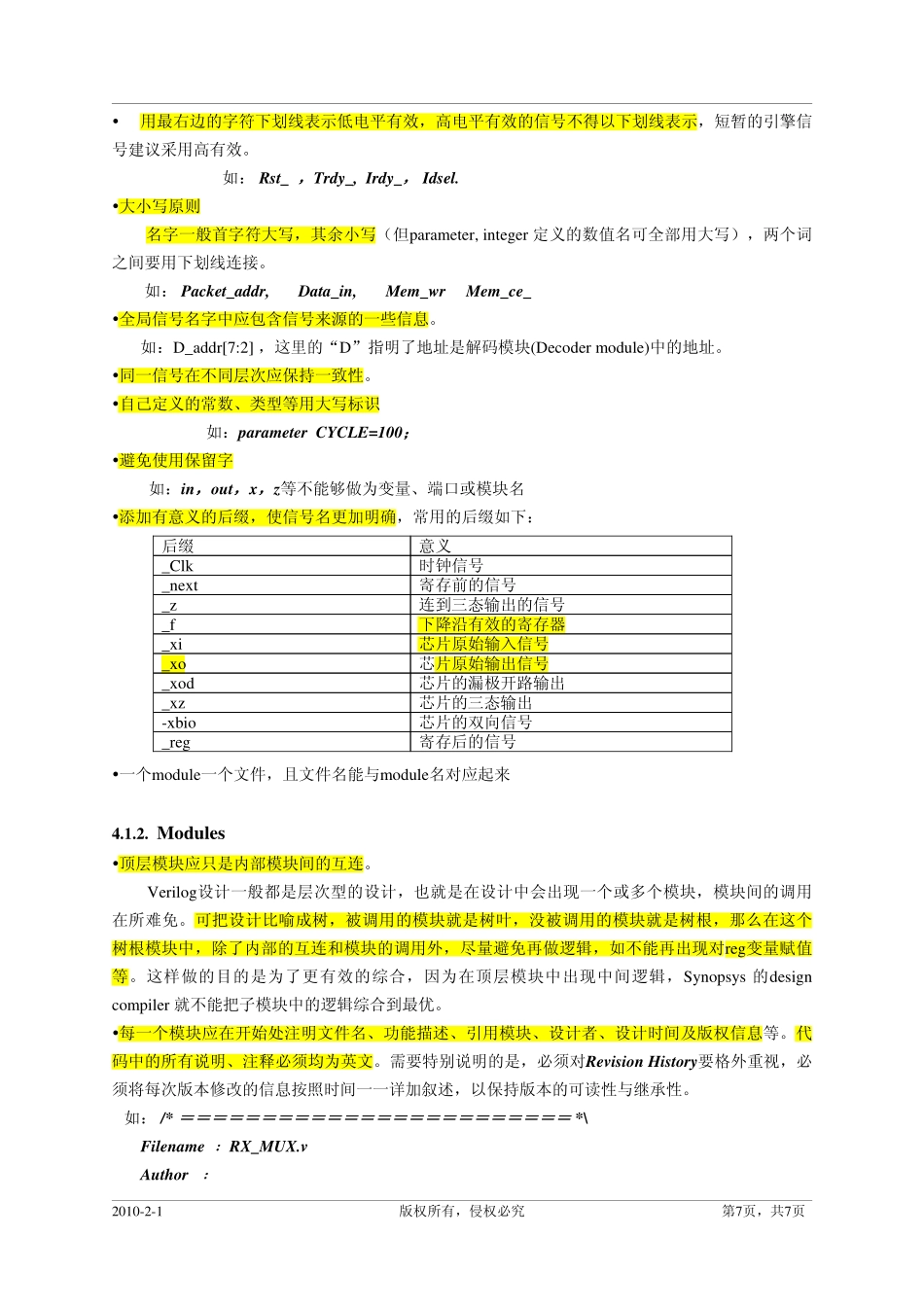

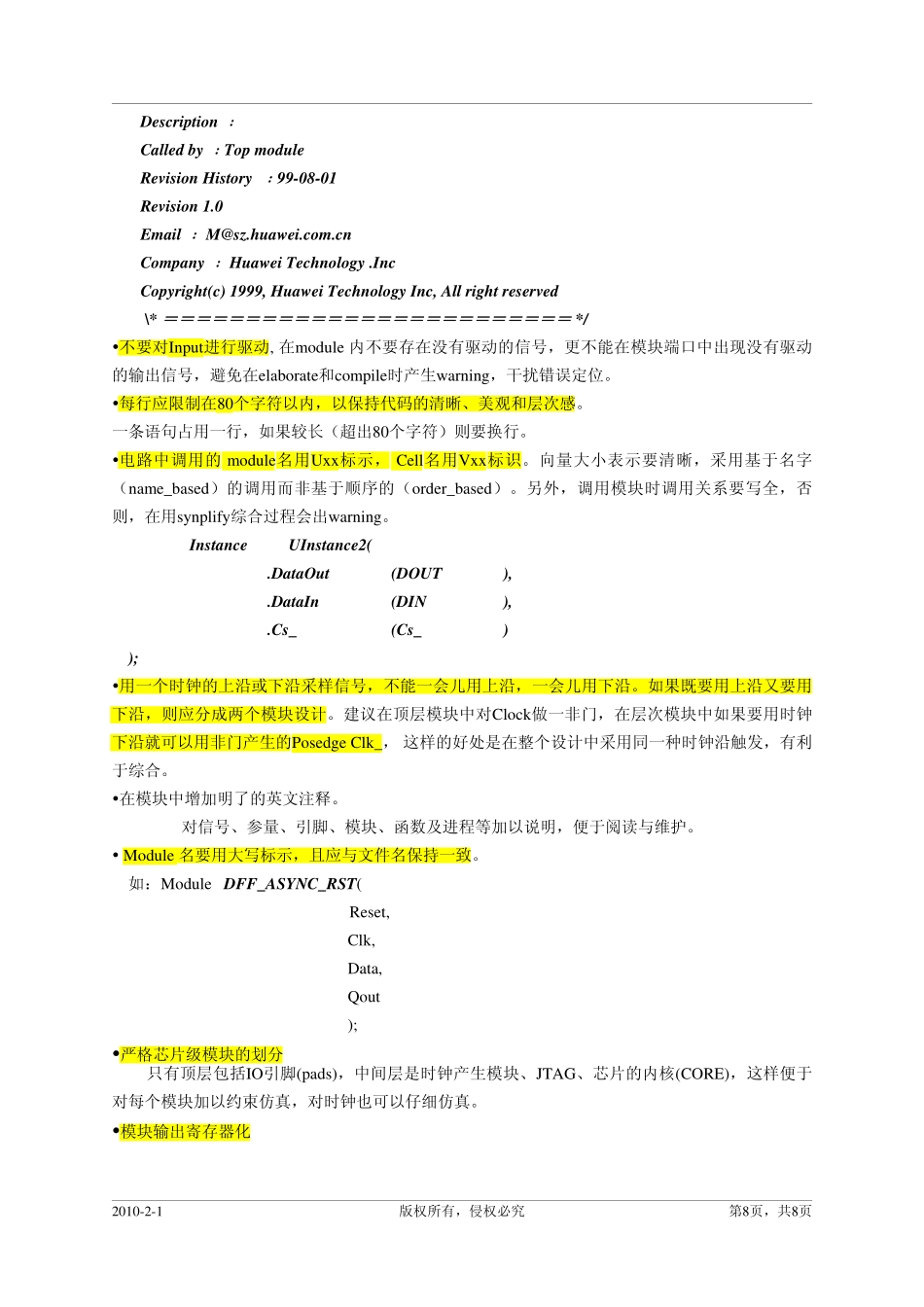

1.目的本规范的目的是提高书写代码的可读性、可修改性、可重用性,优化代码综合和仿真的结果,指导设计工程师使用VerilogHDL规范代码和优化电路,规范化可编程技术部的FPGA设计输入,从而做到:①逻辑功能正确,②可快速仿真,③综合结果最优(如果是hardwaremodel),④可读性较好。2.范围本规范涉及VerilogHDL编码风格,编码中应注意的问题,Testbench的编码等。本规范适用于Verilogmodel的任何一级(RTL,behavioral,gate_level),也适用于出于仿真、综合或二者结合的目的而设计的模块。3.定义VerilogHDL:Verilog硬件描述语言FSM:有限状态机伪路径:静态时序分析(STA)认为是时序失败,而设计者认为是正确的路径。4.规范内容4.1.Verilog编码风格本章节中提到的Verilog编码规则和建议适应于Verilogmodel的任何一级(RTL,behavioral,gate_level),也适用于出于仿真,综合或二者结合的目的而设计的模块。4.1.1.命名的习惯选择有意义的信号和变量名,对设计是十分重要的。命名包含信号或变量诸如出处、有效状态等基本含义,下面给出一些命名的规则。�用有意义而有效的名字有效的命名有时并不是要求将功能描述出来,如For(I=0;I<1024;I=I+1)Mem[I]<=32’b0;For语句中的循环指针I就没必要用loop_index作为指针名。�用连贯的缩写长的名字对书写和记忆会带来不便,甚至带来错误。采用缩写时应注意同一信号在模块中的一致性。缩写的例子如下:AddraddressPntrpointerClkclockreset2010-2-1版权所有,侵权必究第6页,共20页�用最右边的字符下划线表示低电平有效,高电平有效的信号不得以下划线表示,短暂的引擎信号建议采用高有效。如:Rst_,Trdy_,Irdy_,Idsel.�大小写原则名字一般首字符大写,其余小写(但parameter,integer定义的数值名可全部用大写),两个词之间要用下划线连接。如:Packet_addr,Data_in,Mem_wrMem_ce_�全局信号名字中应包含信号来源的一些信息。如:D_addr[7:2],这里的“D”指明了地址是解码模块(Decodermodule)中的地址。�同一信号在不同层次应保持一致性。�自己定义的常数、类型等用大写标识如:parameterCYCLE=100;�避免使用保留字如:in,out,x,z等不能够做为变量、端口或模块名�添加有意义的后缀,使信号名更加明确,常用的后缀如下:寄存后的信号_reg芯片的双向信号-xbio芯片的三态输出_xz芯片的漏极开路输出_xod芯片原始输出信号_xo芯片原始输入信号_xi下降沿有效的寄存器_f连到三态输出的信号_z寄存前的信...