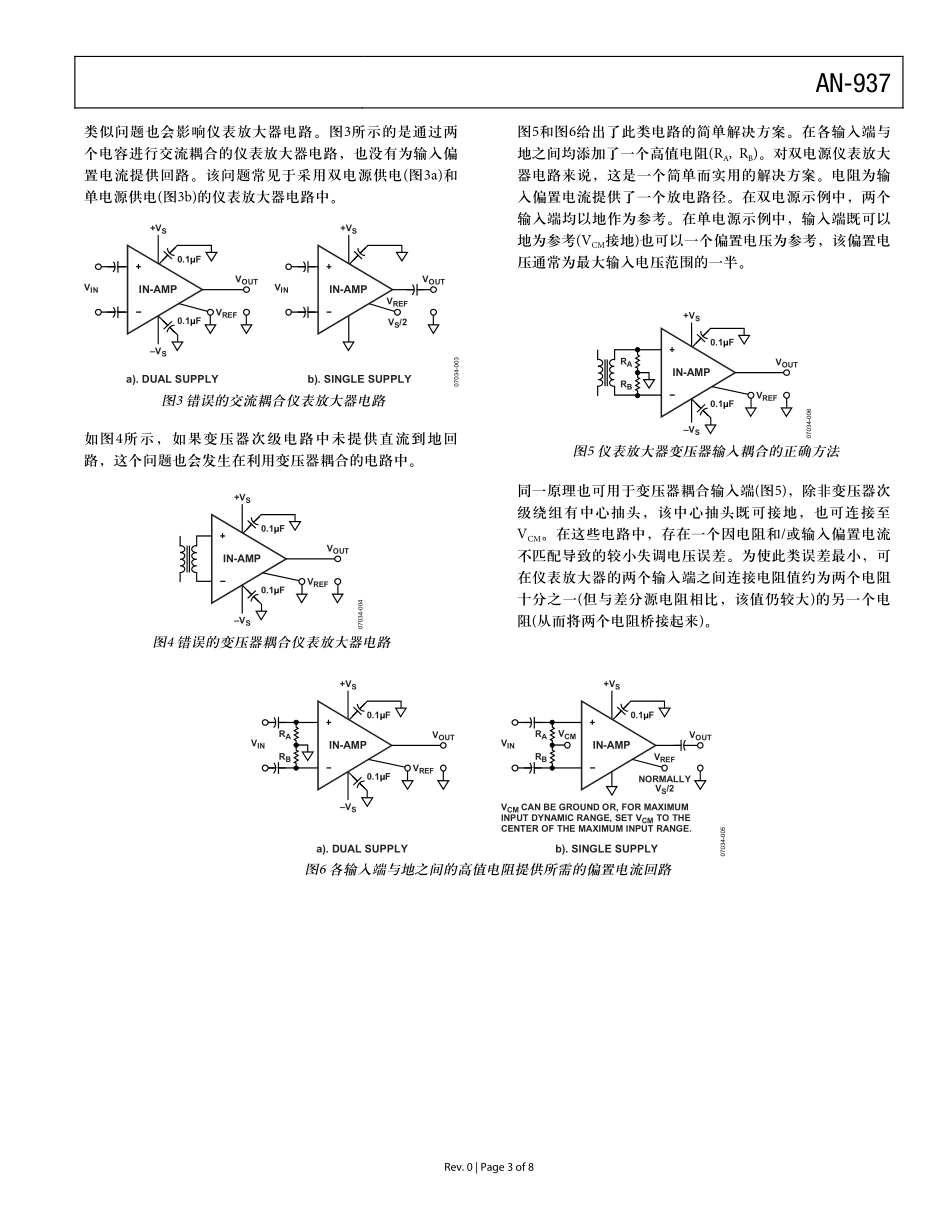

放大器电路设计:如何避免常见问题OneTechnologyWay•P.O.Box9106•Norwood,MA02062-9106•Tel:781/329-4700•Fax:781/326-8703•www.analog.comAN-937应用笔记作者:CharlesKitchinRev.0|Page1of8OPAMP+VS–VS0.1µF0.1µFVINR2VOUTR307034-001简介与分立半导体组件相比,使用运算放大器和仪表放大器能给设计师带来显著优势。虽然有关电路应用的著述颇丰,但由于设计电路时往往匆忙行事,因而忽视了一些基本问题,结果使电路功能与预期不符。本应用笔记论述了最为常见的设计问题并提出了实用的解决方案。缺少直流偏置电流回路最常见的应用问题之一是在交流耦合运算放大器或仪表放大器电路应用中,没有为偏置电流提供直流回路。图1中,一个电容串接在一个运算放大器的同相(+)输入端。这种交流耦合是隔离输入电压(VIN)中的直流电压的一种简单方法。这种方法在高增益应用中尤为有用,在增益较高时,即使是放大器输入端的一个较小直流电压,也会影响运放的动态范围,甚至可能导致输出饱和。然而,容性耦合进高阻抗输入端而不为正输入端中的电流提供直流路径的做法会带来一些问题。这一过程可能较长。例如,对于一个带有场效应晶体管(FET)输入端的放大器,若其偏置电流为1pA,通过一个0.1-μF的电容进行耦合,则其IC充电率I/C为10–12/10–7=10μV/秒合600μV/分。如果增益为100,则输出漂移为0.06V/分。可见,如果采用交流耦合示波器做短时间的测试可能无法检测出这一问题,电路要在数小时后才会发生故障。总之,避免这一问题是非常重要的。输入偏置电流流经耦合电容,给其充电,直到超过放大器输入电路的额定共模电压或超过输出限值。根据输入偏置电流的极性,电容充电或者向正电源电压方向,或者向负电源电压方向。这个偏置电压会被放大器的闭环直流增益放大。图2所示即是这一常见问题的一种简单解决方案。此例中,一个电阻连接在运算放大器的输入端与地之间,从而为输入偏置电流提供了一个回路。为最小化输入偏置电流导致的失调电压,在使用双极性运放的时候,考虑运放两个输入端的匹配问题,通常将R1设为R2和R3的并联值。但要注意的是,该电阻始终会给电路带来一定噪声,因而需在电路输入阻抗、所需输入耦合电容大小与电阻引进的约翰逊噪声之间进行权衡。典型电阻值一般在100,000Ω至1MΩ之间。OPAMP+VS–VS0.1µF0.1µFVINR2R1C1VOUTR3DESIGNEQUATIONS–3dBINPUTBW=1/(2πR1C1)R1ISTYPICALLYSETEQUALTOTHEPARALLELCOMBINATIONOFR2ANDR3.07034-002...