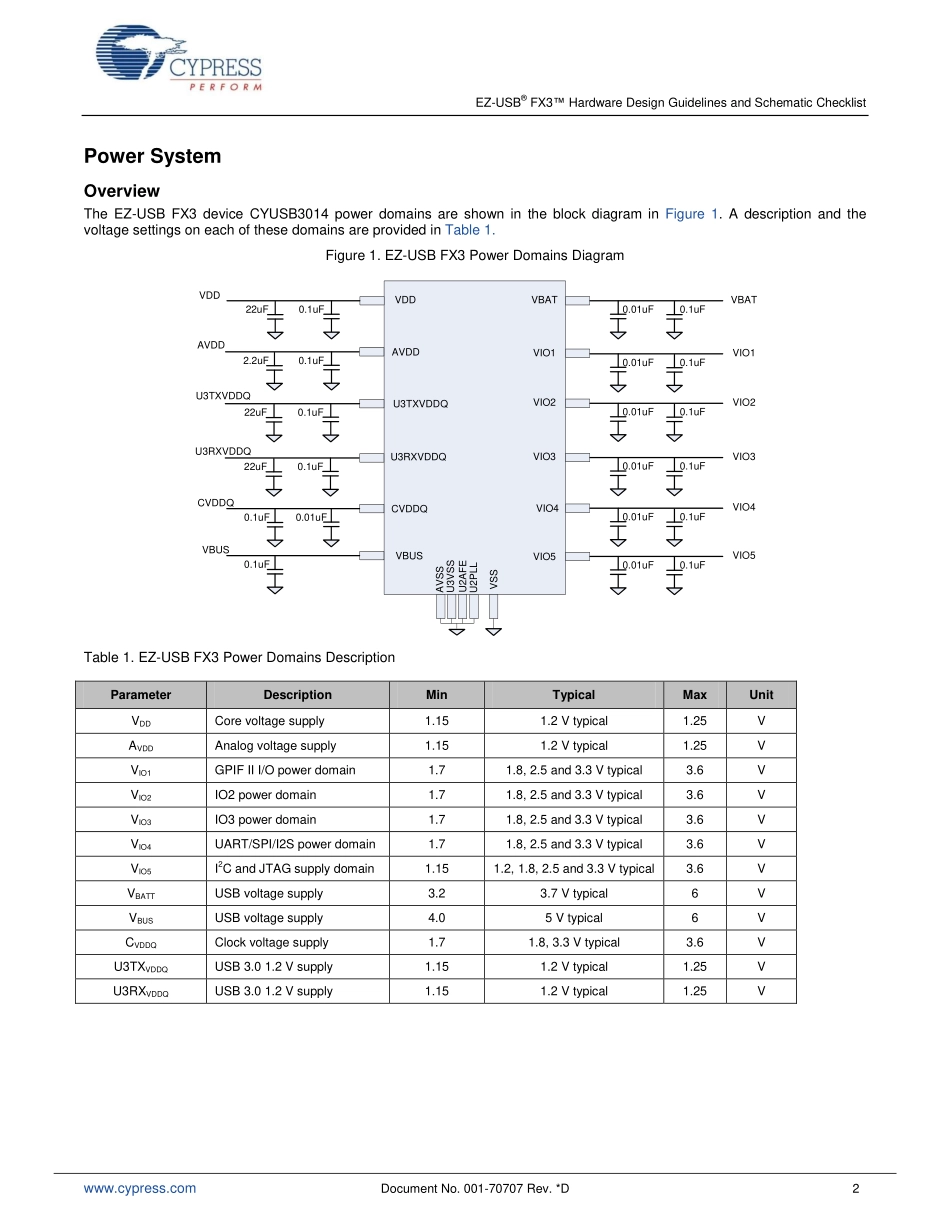

www.cypress.comDocumentNo.001-70707Rev.*D1AN70707EZ-USB®FX3™HardwareDesignGuidelinesandSchematicChecklistAuthor:RizwanAfridi,HusseinOsmanAssociatedProject:NoAssociatedPartFamily:CYUSB3014SoftwareVersion:N/ARelatedApplicationNotes:NoneAN70707discussesrecommendedpracticesforEZ-USB®FX3™hardwaredesignandthecriticalitemsthatadevelopermustconsider.TheCypressEZ-USBFX3isthenextgenerationUSB3.0peripheralcontroller.Withitshighlyintegratedandflexiblefeatures,developerscanaddUSB3.0functionalitytoanysystem.ContentsIntroduction.......................................................................1PowerSystem...................................................................2Overview......................................................................2PowerModes...............................................................3DeviceSupplyDecoupling............................................3InrushCurrentConsiderationandPowerSupplyDesign..............................................................3Clocking............................................................................5Crystal..........................................................................5Clock............................................................................6WatchdogTimer...........................................................6GPIFIIInterface................................................................6I2CInterface......................................................................6LowPerformancePeripherals(LPP).................................7JTAG............................................................................7I2S.................................................................................7SPIandUART..............................................................7Booting..............................................................................7EMIandESDConsiderations............................................7FX3DevicePackageDimensions.............................