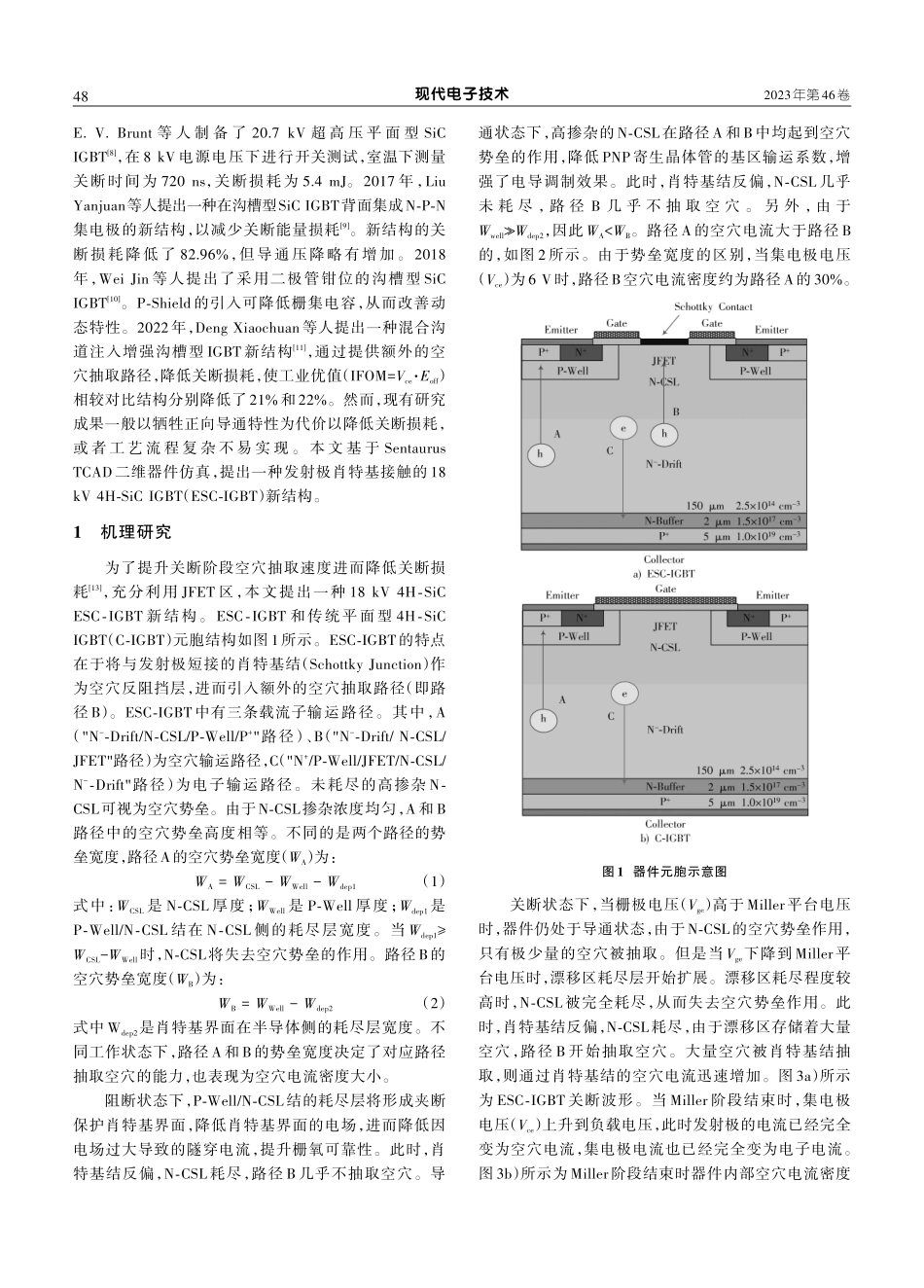

现代电子技术ModernElectronicsTechniqueSep.2023Vol.46No.182023年9月15日第46卷第18期2020年,我国政府提出加速“新基建”进度[1]。“新基建”中的设施建设需要大量的功率半导体器件,尤其是在智能电网、工业级电源、高速动车牵引、舰载武器等超高压应用领域[2]。目前,硅功率器件是功率器件主力军,在耐压能力、工作频率以及转换效率等方面均接近理论极限[3‐4]。随着超高压电力电子系统在高耐压、高功率、高开关速度、高工作温度以及小体积等方面提出更高的要求,硅功率器件的局限性越发明显。碳化硅(SiliconCarbide,SiC)相比硅具有更大的禁带宽度、更高的临界击穿电场和热导率等优异的材料特性[5‐6],并且也可以通过热氧化直接形成二氧化硅(SiliconDioxide,SiO2)层。SiC绝缘栅双极晶体管(InsulatedGateBipolarTransistor,IGBT)兼顾SiC材料优势以及高输入阻抗、高阻断电压、强电流输运能力、易于驱动等器件优势[7],在超高压应用领域(≥15kV)具有不可替代的地位。近年来,SiCIGBT关断损耗一直是研究关注的热点。2014年,DOI:10.16652/j.issn.1004‐373x.2023.18.009引用格式:张莉,陈致宇.18kV4H‐SiCESC‐IGBT结构设计与特性研究[J].现代电子技术,2023,46(18):47‐52.18kV4H⁃SiCESC⁃IGBT结构设计与特性研究张莉,陈致宇(中国电子科技集团公司第二十九研究所四川省高效电源变换技术工程研究中心,四川成都610036)摘要:针对碳化硅(SiC)绝缘栅双极晶体管(IGBT)空穴抽取慢,导致关断损耗高的问题,文中提出一种发射极肖特基接触的18kV4H‐SiCIGBT(ESC‐IGBT)新结构。该结构在JFET区上方引入肖特基结,并将其与发射极短接,提供额外的空穴抽取路径,降低关断损耗。当ESC‐IGBT处于关断阶段时,随着耗尽层在漂移区中扩展,额外的空穴抽取路径开始工作,可以有效解决单一路径空穴抽取慢的问题,进而降低关断损耗。SentaurusTCAD分析结果表明:ESC‐IGBT击穿电压为20.9kV时,所提出的ESC‐IGBT的栅氧化层电场相比传统平面型有效降低46%,栅氧可靠性有所提高;在正向导通特性无明显退化的前提下,ESC‐IGBT栅集电荷比传统平面型SiCIGBT结构降低37%,关断损耗和工业优值(IFOM=Vce·Eoff)降低34%。另外,ESC‐IGBT易实现的工艺与主流SiCIGBT工艺兼容,适用于高频高可靠性电力电子系统。关键词:ESC‐IGBT;SiCIGBT;空穴抽取路径;肖特基接触工艺;栅氧可靠性;关断损耗中图分类号:TN322+.8‐34文献标识码:A文章编号:100...