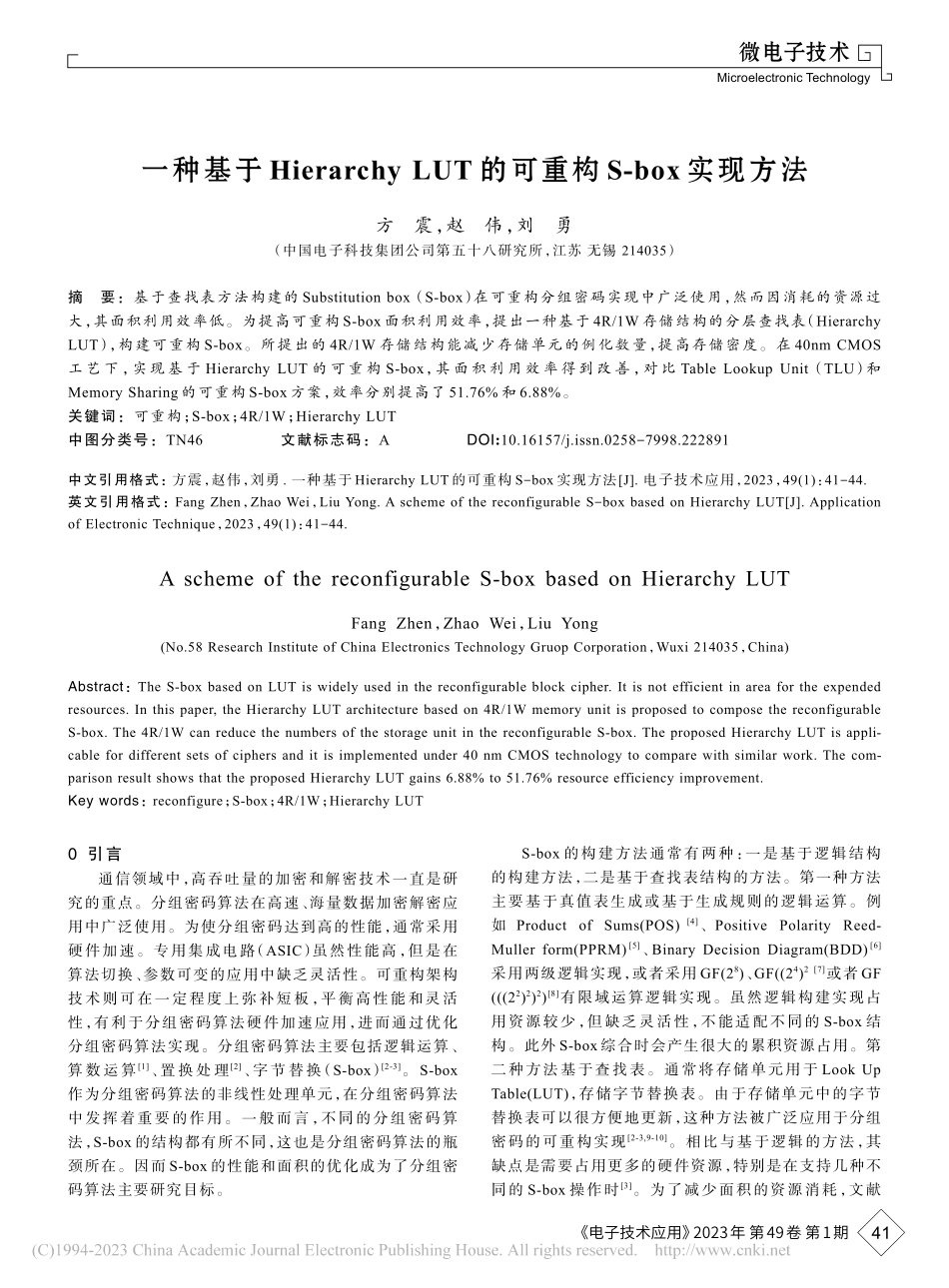

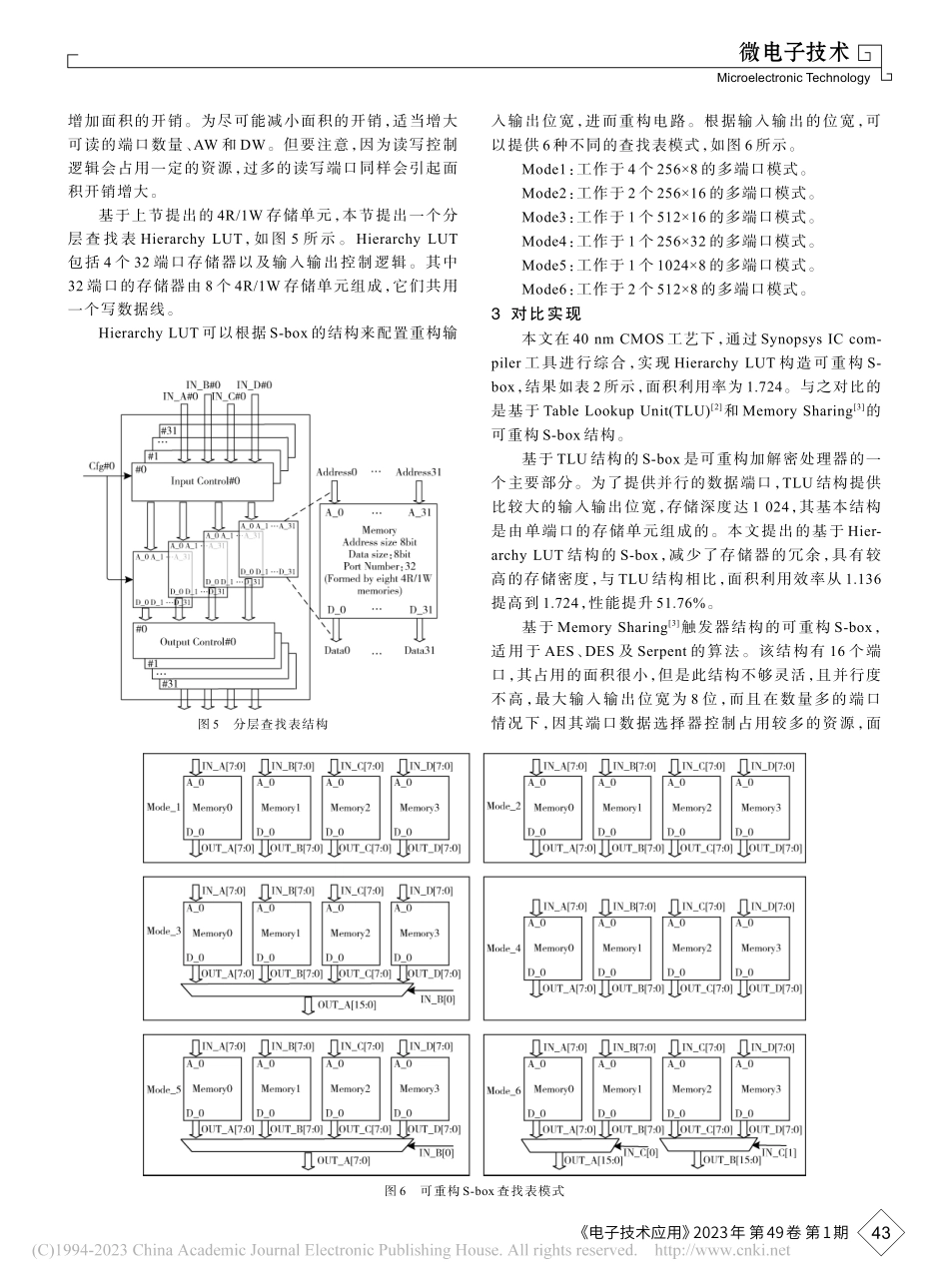

《电子技术应用》2023年第49卷第1期MicroelectronicTechnology微电子技术一种基于HierarchyLUT的可重构S-box实现方法方震,赵伟,刘勇(中国电子科技集团公司第五十八研究所,江苏无锡214035)摘要:基于查找表方法构建的Substitutionbox(S-box)在可重构分组密码实现中广泛使用,然而因消耗的资源过大,其面积利用效率低。为提高可重构S-box面积利用效率,提出一种基于4R/1W存储结构的分层查找表(HierarchyLUT),构建可重构S-box。所提出的4R/1W存储结构能减少存储单元的例化数量,提高存储密度。在40nmCMOS工艺下,实现基于HierarchyLUT的可重构S-box,其面积利用效率得到改善,对比TableLookupUnit(TLU)和MemorySharing的可重构S-box方案,效率分别提高了51.76%和6.88%。关键词:可重构;S-box;4R/1W;HierarchyLUT中图分类号:TN46文献标志码:ADOI:10.16157/j.issn.0258-7998.222891中文引用格式:方震,赵伟,刘勇.一种基于HierarchyLUT的可重构S-box实现方法[J].电子技术应用,2023,49(1):41-44.英文引用格式:FangZhen,ZhaoWei,LiuYong.AschemeofthereconfigurableS-boxbasedonHierarchyLUT[J].ApplicationofElectronicTechnique,2023,49(1):41-44.AschemeofthereconfigurableS-boxbasedonHierarchyLUTFangZhen,ZhaoWei,LiuYong(No.58ResearchInstituteofChinaElectronicsTechnologyGruopCorporation,Wuxi214035,China)Abstract:TheS-boxbasedonLUTiswidelyusedinthereconfigurableblockcipher.Itisnotefficientinareafortheexpendedresources.Inthispaper,theHierarchyLUTarchitecturebasedon4R/1WmemoryunitisproposedtocomposethereconfigurableS-box.The4R/1WcanreducethenumbersofthestorageunitinthereconfigurableS-box.TheproposedHierarchyLUTisappli‐cablefordifferentsetsofciphersanditisimplementedunder40nmCMOStechnologytocomparewithsimilarwork.Thecom‐parisonresultshowsthattheproposedHierarchyLUTgains6.88%to51.76%resourceefficiencyimprovement.Keywords:reconfigure;S-box;4R/1W;HierarchyLUT0引言通信领域中,高吞吐量的加密和解密技术一直是研究的重点。分组密码算法在高速、海量数据加密解密应用中广泛使用。为使分组密码达到高的性能,通常采用硬件加速。专用集成电路(ASIC)虽然性能高,但是在算法切换、参数可变的应用中缺乏灵活性。可重构架构技术则可在一定程度上弥补短板,平...