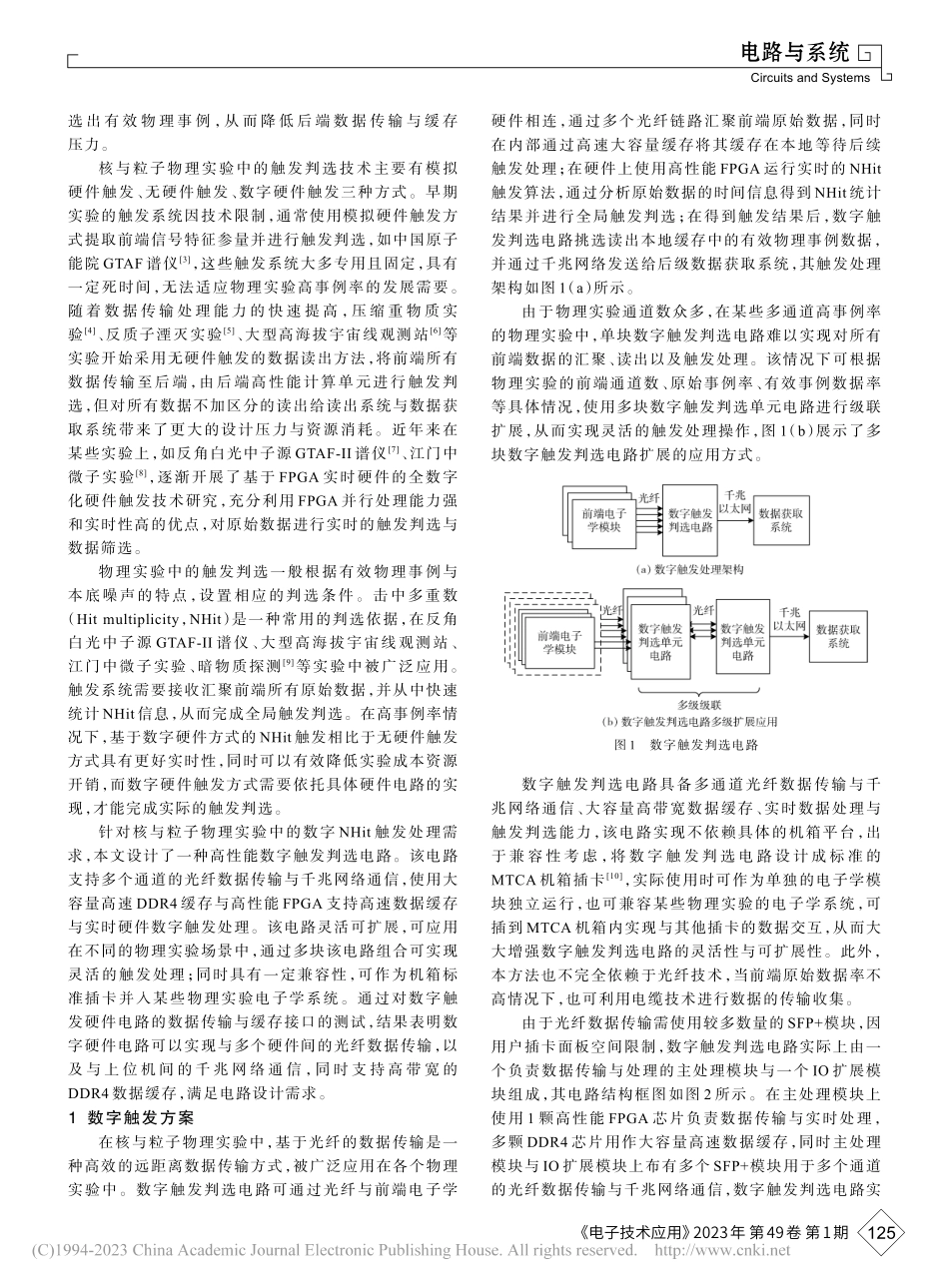

www.ChinaAET.comCircuitsandSystems电路与系统一种用于核与粒子物理实验数字化的多重数触发判选电路设计*刘尚铭1,2,曹平1,2,李超1,2,汪晓虎1,2(1.中国科学技术大学核探测与核电子学国家重点实验室,安徽合肥230026;2.中国科学技术大学近代物理系,安徽合肥230026)摘要:核与粒子物理实验中,因实验本底与探测器噪声影响,实验需要通过触发判选机制筛选出有效物理事例,剔除掉本底噪声。针对物理实验高事例率情况下基于击中多重数(Hitmultiplicity,NHit)的触发判选需求,设计了一种高性能数字触发判选电路。该电路具有13路高速串行通信接口,支持光纤数据传输与千兆网络通信;板载32GbDDR4缓存与高性能FPGA,以支持大容量高速存储与实时数据处理。基于该电路可运行实时的硬件NHit触发算法,从而实现对前端数据的快速触发判选与数据读出,同时该电路便于扩展,可灵活地用在不同的物理实验上。经过测试验证,数字触发判选电路单路光纤接口传输速率可达8.125Gb/s,上行网络传输速率达949.3Gb/s,DDR4缓存实际读写速率可达102.6Gb/s,满足数字触发判选电路设计的数据传输与缓存需求。关键词:触发判选;数据读出;光纤;SiTCP;DDR中图分类号:TL822+.3文献标志码:ADOI:10.16157/j.issn.0258-7998.222927中文引用格式:刘尚铭,曹平,李超,等.一种用于核与粒子物理实验数字化的多重数触发判选电路设计[J].电子技术应用,2023,49(1):124-129.英文引用格式:LiuShangming,CaoPing,LiChao,etal.DesignofadigitalNHittriggercircuitfornuclearandparticlephysicsexperiment[J].ApplicationofElectronicTechnique,2023,49(1):124-129.DesignofadigitalNHittriggercircuitfornuclearandparticlephysicsexperimentLiuShangming1,2,CaoPing1,2,LiChao1,2,WangXiaohu1,2(1.StateKeyLaboratoryofParticleDetectionandElectronics,UniversityofScienceandTechnologyofChina,Hefei230026,China;2.DepartmentofModernPhysics,UniversityofScienceandTechnologyofChina,Hefei230026,China)Abstract:Innuclearandparticlephysicsexperiments,duetotheinfluenceoftheexperimentalbackgroundanddetectornoise,theexperimentneedstopickoutvalidphysicaleventsbythetriggerselection,andeliminatethebackgroundnoise.Aimingatthetriggerselectionrequirementsbasedonhitmultiplicity(NHit)inthecasesofhigheventratesinphysicalexp...