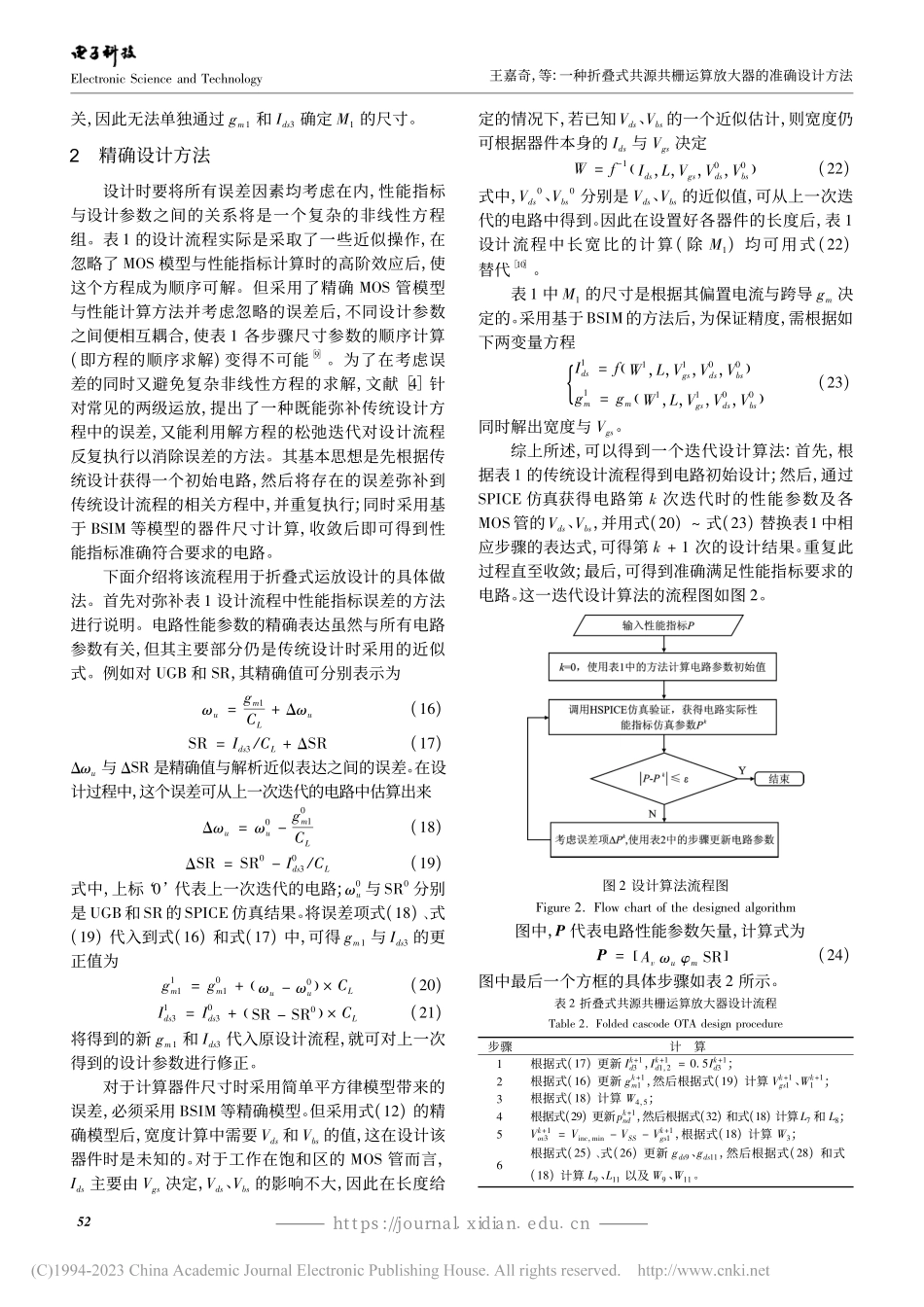

2023年第36卷第3期ElectronicSci.&Tech./Mar.15,2023https://journal.xidian.edu.cn收稿日期:2021-09-13基金项目:国家自然科学基金(60672013)NationalNaturalScienceFoundationofChina(60672013)作者简介:王嘉奇(1994-),男,硕士研究生。研究方向:模拟集成电路设计。吕高崇(1996-),女,硕士研究生。研究方向:模拟集成电路设计。郭裕顺(1965-),男,教授。研究方向:电路与系统。一种折叠式共源共栅运算放大器的准确设计方法王嘉奇,吕高崇,郭裕顺(杭州电子科技大学电子信息学院,浙江杭州310018)摘要传统折叠式共源共栅放大器的人工设计流程只能得到近似的设计结果,优化方法获得的结果较好,但需耗费大量计算。文中针对这类放大器,给出了一种准确设计方法。通过SPICE仿真弥补传统设计流程各性能指标解析近似产生的误差,同时采用基于BSIM模型的器件尺寸计算,反复执行这一设计流程,消除了传统设计过程存在的误差,得到准确的设计结果。文中所提方法相较于传统人工方法更精确,避免了设计时的反复调试;与优化方法相比,虽仍要通过一个迭代过程,但因收敛较快,故计算量较小。文中以0.18μm与90nm实际工艺库下的电路设计为例,给出了仿真设计结果,证明了所提方法的正确性与有效性。关键词模拟IC设计;运算放大器;模拟设计自动化;电路优化设计;器件尺寸;BSIM模型;共源共栅放大器;迭代设计方法中图分类号TN402文献标识码A文章编号1007-7820(2023)03-050-06doi:10.16180/j.cnki.issn1007-7820.2023.03.008AnAccurateDesignApproachfortheFoldedCascodeOperationalAmplifierWANGJiaqi,LÜGaochong,GUOYushun(SchoolofElectronicsandInformationEngineering,HangzhouDianziUniversity,Hangzhou310018,China)AbstractTheresultsobtainedfromthetraditionaldesignprocedureofthefoldedcascodeamplifierareinaccu-rate.Theoptimizationmethodcanproducefairlyaccuratedesignresults,butconsumeslargeamountofcomputations.Thisstudypresentsanaccuratedesignmethodforthiskindofamplifier.ThroughSPICEsimulation,theerrorscausedbytheanalysisandapproximationofvariousperformanceindicatorsinthetraditionaldesignprocessarecom-pensated.Atthesametime,ThedevicesizecalculationbasedontheBSIMmodelisadopted,andthisdesignprocessisrepeatedlyexecuted,whichgraduallyeliminatestheerrorsexistinginthetraditionaldesignpr...