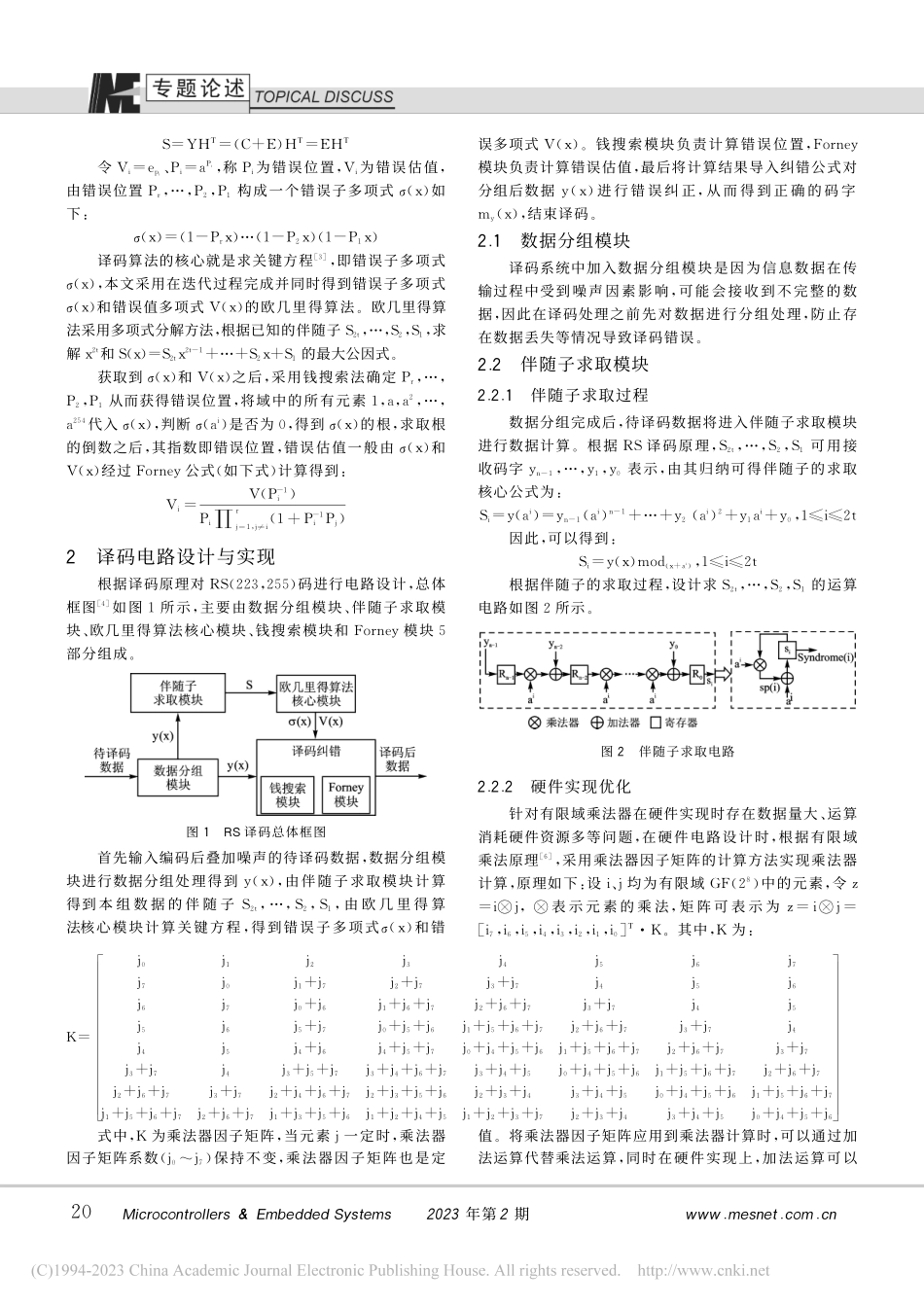

敬请登录网站在线投稿(tougao.mesnet.com.cn)2023年第2期19在FPGA上实现对RS译码器的优化设计李锦明,张萍萍(中北大学半导体与物理学院,太原030051)摘要:针对里德所罗门码(ReedSolomon,RS)译码在硬件实现时存在数据量大、消耗资源多等问题,基于CCSDS标准中的RS(255,223)码,根据欧几里得核心译码算法,在FPGA上实现对RS译码器的优化设计。本文提出采用乘法器因子矩阵方法将有限域中的乘法计算转换为加法运算,用异或操作在硬件中实现,简化硬件运算数据量;在欧几里得算法核心模块实现中,采用多项式除法电路和多项式乘法电路进行硬件电路设计,降低运算复杂度,可以有效节约硬件资源。通过FPGA测试验证,优化设计的译码器可以有效译码并具有较好的译码性能,完成最多16个码元数据的纠错。关键词:里德所罗门码;译码器;欧几里得算法;FPGA中图分类号:TP2文献标识码:AOptimizationDesignofRSDecoderBasedonFPGALiJinming,ZhangPingping(SchoolofSemiconductorsandPhysics,NorthUniversityofChina,Taiyuan030051,China)Abstract:AimingattheproblemsoflargedatavolumeandresourceconsumptioninthehardwareimplementationofReedSolomon(RS)decoding,theRSdecoderisoptimizedinFPGAimplementationbasedontheRS(255,223)codeinCCSDSstandardandEuclidcoredeco-dingalgorithm.Inthisdesign,themultiplierfactormatrixmethodisproposedtoconvertthemultiplicationcalculationinthefinitefieldtotheadditionoperation,andtheexclusiveORoperationisimplementedinhardwaretosimplifytheamountofhardwareoperatio...