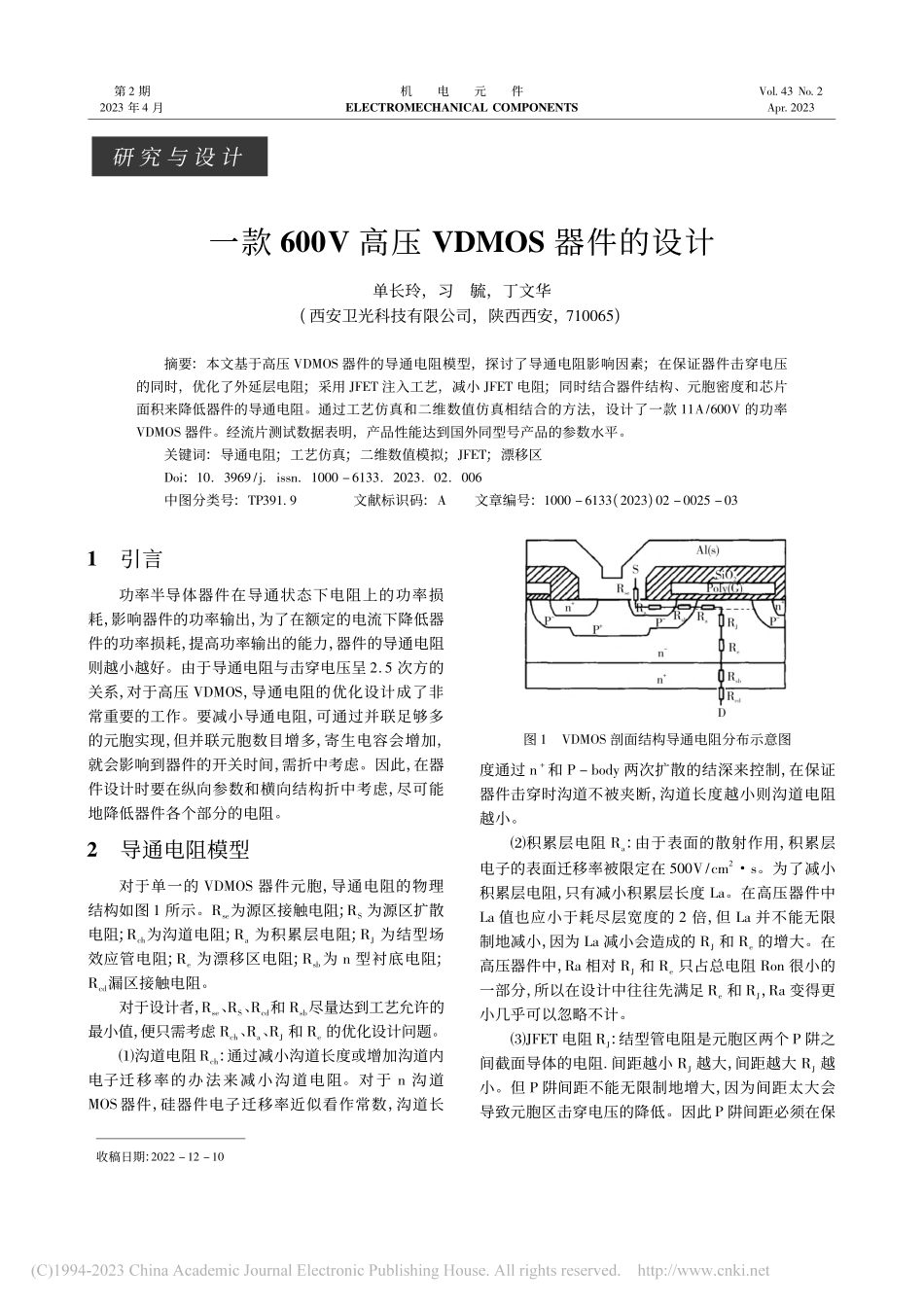

第2期2023年4月机电元件ELECTROMECHANICALCOMPONENTSVol.43No.2Apr.2023收稿日期:2022-12-10研究与设计一款600V高压VDMOS器件的设计单长玲,习毓,丁文华(西安卫光科技有限公司,陕西西安,710065)摘要:本文基于高压VDMOS器件的导通电阻模型,探讨了导通电阻影响因素;在保证器件击穿电压的同时,优化了外延层电阻;采用JFET注入工艺,减小JFET电阻;同时结合器件结构、元胞密度和芯片面积来降低器件的导通电阻。通过工艺仿真和二维数值仿真相结合的方法,设计了一款11A/600V的功率VDMOS器件。经流片测试数据表明,产品性能达到国外同型号产品的参数水平。关键词:导通电阻;工艺仿真;二维数值模拟;JFET;漂移区Doi:10.3969/j.issn.1000-6133.2023.02.006中图分类号:TP391.9文献标识码:A文章编号:1000-6133(2023)02-0025-031引言功率半导体器件在导通状态下电阻上的功率损耗,影响器件的功率输出,为了在额定的电流下降低器件的功率损耗,提高功率输出的能力,器件的导通电阻则越小越好。由于导通电阻与击穿电压呈2.5次方的关系,对于高压VDMOS,导通电阻的优化设计成了非常重要的工作。要减小导通电阻,可通过并联足够多的元胞实现,但并联元胞数目增多,寄生电容会增加,就会影响到器件的开关时间,需折中考虑。因此,在器件设计时要在纵向参数和横向结构折中考虑,尽可能地降低器件各个部分的电阻。2导通电阻模型对于单一的VDMOS器件元胞,导通电阻的物理结构如图1所示。Rse为源区接触电阻;RS为源区扩散电阻;Rch为沟道电阻;Ra为积累层电阻;RJ为结型场效应管电阻;Re为漂移区电阻;Rsb为n型衬底电阻;Rcd漏区接触电阻。对于设计者,Rse、RS、Rcd和Rsb尽量达到工艺允许的最小值,便只需考虑Rch、Ra、RJ和Re的优化设计问题。⑴沟道电阻Rch:通过减小沟道长度或增加沟道内电子迁移率的办法来减小沟道电阻。对于n沟道MOS器件,硅器件电子迁移率近似看作常数,沟道长图1VDMOS剖面结构导通电阻分布示意图度通过n+和P-body两次扩散的结深来控制,在保证器件击穿时沟道不被夹断,沟道长度越小则沟道电阻越小。⑵积累层电阻Ra:由于表面的散射作用,积累层电子的表面迁移率被限定在500V/cm2·s。为了减小积累层电阻,只有减小积累层长度La。在高压器件中La值也应小于耗尽层宽度的2倍,但La并不能无限制地减小,因为La减小会造成的RJ和Re的增大。在高压器件中,Ra相对RJ和Re只占总电阻Ron很小的一部分,所以在设计中往往先满足...