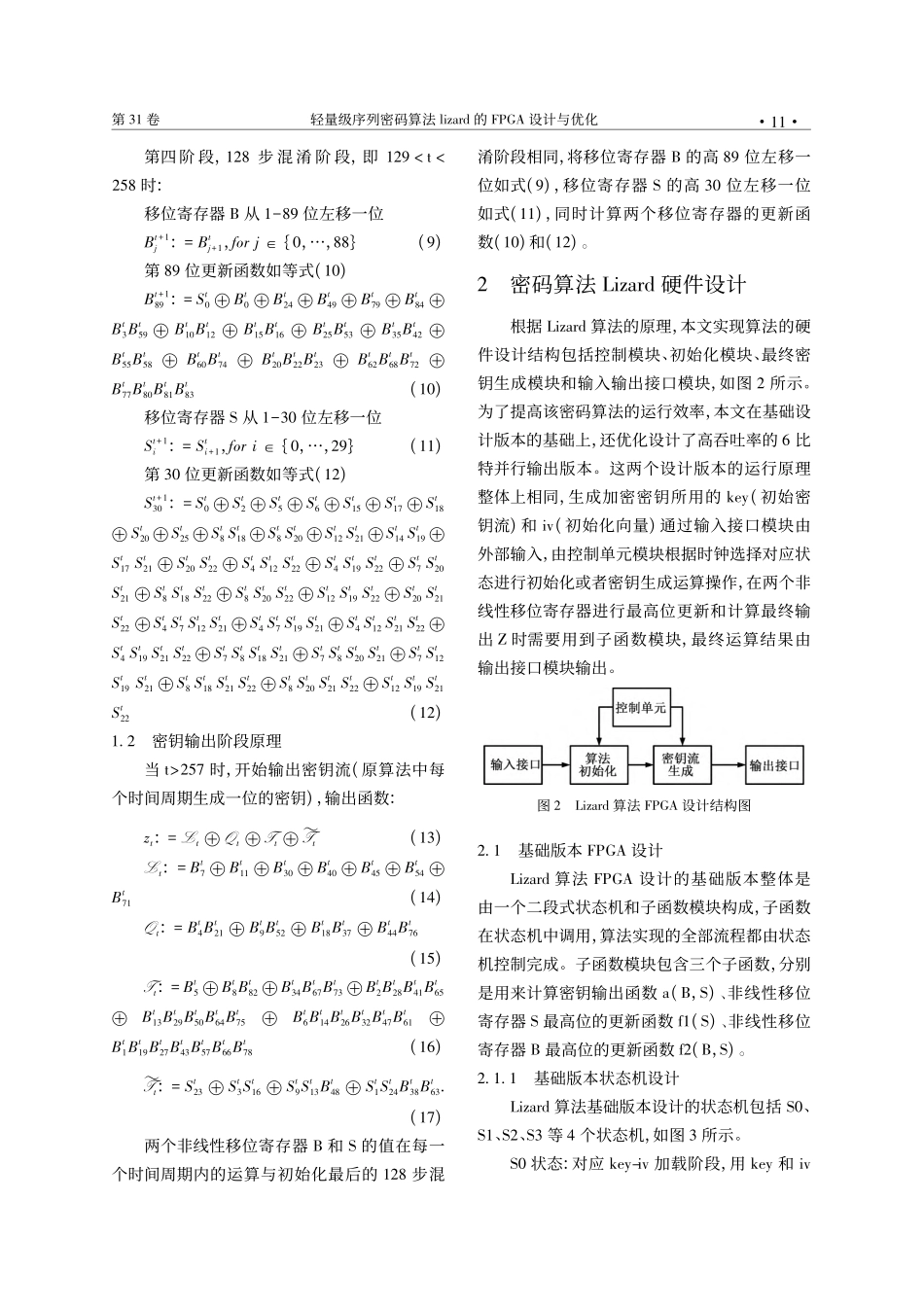

第31卷第1期北京电子科技学院学报2023年3月Vol.31No.1JournalofBeijingElectronicScienceandTechnologyInstituteMar.2023轻量级序列密码算法lizard的FPGA设计与优化*肖超恩仓晓彤张磊北京电子科技学院,北京市100070摘要:Lizard序列密码算法作为类似eSTREAM组合中Grain的算法,由于较小的内部状态,具有较好的硬件实现优势。为了在硬件层面提高该算法实现的工作频率,同时一定程度上降低资源消耗,本文使用Verilog硬件语言对该算法进行FPGA实现,并提出两种设计方案。首先,本文基于二段式有限状态机设计了算法实现的基础版本。其次,本文在基础版本设计的基础上通过对密码Lizard算法的原理分析,完成了算法6比特并行版本的设计,进一步提高了算法运行的吞吐率。最后,在Vivado2019.2.1环境中采用赛灵思公司的Spartan7系列的硬件平台XC7S50FGGA484-1芯片,使用Verilog硬件设计语言对密码Lizard算法两种设计版本进行设计、综合和实现,再通过ModelSim10.4进行仿真验证,结果表明两种设计的工程实现结果与标准测试向量相同。性能测试结果显示:在基础版本中,Lizard序列密码算法实现了最小的面积消耗,最高工作频率达到221MHz;在并行版本中,Lizard序列密码算法实现最大的吞吐量可达1254Mbps,提高了数据加密运算的速率。关键词:轻量级;流密码;现场可编程门阵列;并行优化中图分类号:TP393文献标识码:A文章编号:1672-464X(2023)1-09-18*基金项目:国家重点研发计划基金资助项目(项目编号:2017YFB0801803);教育部新工科研究与实践项目(项目编号:E-AQ-GABQ20202704);北京高等教育“本科教学改革创新项目”(项目编号:202110018002);北京电子科技学院一流学科建设项目(项目编号:20210064Z0401、20210056Z0402)**作者简介:肖超恩(1982-),男,湖南人,讲师,博士,主要研究方向为嵌入式系统及网络空间安全。仓晓彤(1999-),男,大学本科。张磊(1979-),男,河北人,正高级工程师,博士,主要研究方向为芯片安全。0引言在保护数字通信方面,流密码有很长的应用历史。1987年,RonaldL.Rivest设计了RC4[1](RivestCipher4),后来被用于SSL(SecureSocketsLayer)/TLS(TransportLayerSecurity)、无线网络安全协议WEP(WiredEquivalentPriva-cy)和TKIP(TemporalKeyIntegrityProtocol)。另外,还有蓝牙标准的E0和GSM(GlobalSystemforMobilecommunication)的A5/1等著名的流密码[2]。然而,E0和A5/1已经被证明是非常不安全的,RC4也显示出严重的漏...