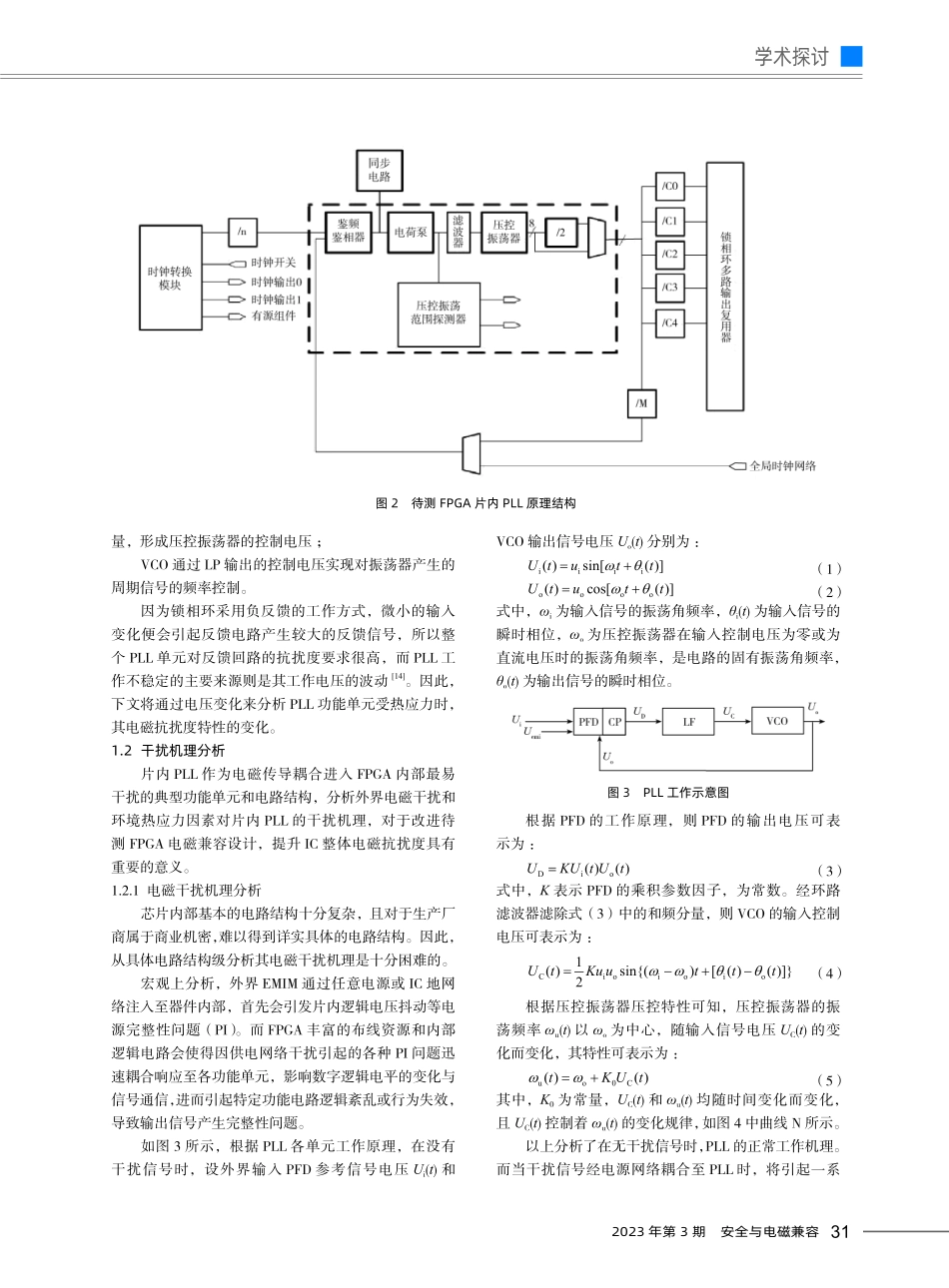

学术探讨292023年第3期安全与电磁兼容0引言随着5G、人工智能、物联网、大数据及其在高速通信、无人系统、工业互联网、先进能源、先进空天等领域的广泛应用,各类装备面临严峻的电磁安全问题[1]。电磁兼容(EMC)问题作为电磁安全的重要组成,逐渐从系统级和设备级不断向着电路模块级、电路板级和元器件层级深入发展[2]。在元器件层级上,集成电路作为典型代表,随着制造工艺和半导体技术的发展,金属-氧化物-半导体(MOS)器件尺寸的不断缩小,芯片集摘要:针对集成电路(IC)在复杂物理环境中的电磁抗扰度漂移问题,研究了环境热应力对基于供电网络传导耦合的现场可编程逻辑门阵列(FPGA)内嵌锁相环(PLL)电路电磁抗扰度的影响。分析典型FPGA片内PLL的功能原理及电磁干扰机理;将环境热应力干扰因素引入PLL电磁抗扰度测试研究中,设计基于电磁干扰直接功率注入(DPI)与热应力耦合的抗扰度测试平台;测试分析了在20~110℃热应力范围内,电磁干扰分别通过1.2V、2.5V和IC地电源网络注入片内PLL时,其电磁抗扰度特性变化。结果表明,当片内PLL功能单元受到不同注入路径的电磁干扰时,其在不同频段的电磁抗扰度变化趋势基本一致;考虑热应力因素影响时,片内PLL的电磁抗扰度特性会发生明显漂移,且当锁相环的2.5V工作电压受到电磁-热复合应力干扰时,PLL的电磁抗扰度最弱,热应力干扰因素加剧了其抗扰度的漂移。关键词:集成电路;锁相环;电磁抗扰度;热应力引用格式:程俊平,李鹏程,沈小奇,等.FPGA片内PLL电磁抗扰度的热应力效应测试分析[J].安全与电磁兼容,2023(3):29-36.ChengJunping,LiPengcheng,ShenXiaoqi,etal.TestandAnalysisofThermalStressEffectontheElectromagneticImmunityforPLLofFPGA[J].SAFETY&EMC,2023(3):29-36.(inChinese)Abstract:TosolvetheElectromagneticImmunitydriftproblemofIntegrateCircuit(IC)incomplexphysicalenvironment,theinfluenceofambientthermalstressonelectromagneticimmunityofaFieldProgrammableGateArray(FPGA)embeddedPhaseLockedLoop(PLL)basedontheconductioncouplingofthepowersupplynetworkisinvestigated.ThefunctionalprincipleandelectromagneticinterferencemechanismofPLLonFPGAchipareanalyzed.TheenvironmentalthermalstressinterferencefactorwasintroducedintothestudyofPLLelectromagneticimmunitytest,andanimmunitytestplatformwasdesignedbasedonthecouplingofdirectpowerinjection(DPI)a...