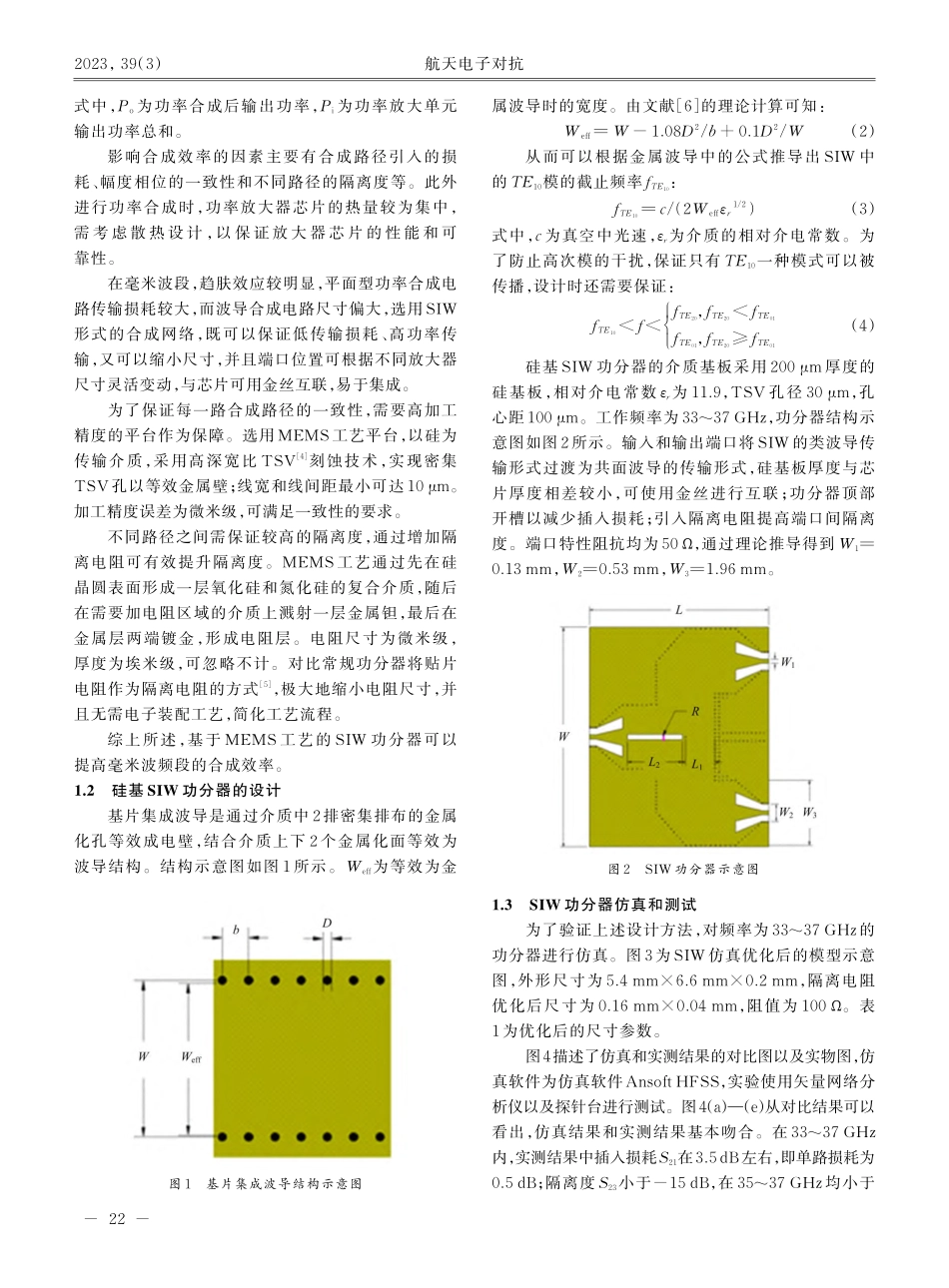

·工程应用·航天电子对抗2023年第3期毫米波功率合成技术及三维堆叠封装朱啸宇,干书剑,赵超,王培阳,孟超,王志奎,胡梦婕(中国航天科工集团8511研究所,江苏南京210007)摘要:为了在毫米波段内实现更大的功率输出,提出了一种毫米波功率合成技术及三维堆叠封装。基于MEMS工艺平台,设计了硅基基片集成波导功分器,在33~37GHz实现了20W的功率合成;利用晶圆级键合技术,将功分器和功率放大器进行三维堆叠封装,实现小型化和高密度集成,并通过实验验证了毫米波大功率合成以及三维堆叠封装的可行性。关键词:毫米波;三维堆叠;基片集成波导;功率合成;晶圆级键合中图分类号:TN928文献标志码:AThepower⁃combiningtechnologyand3Dstackedpackageinmillimeter⁃wavebandZhuXiaoyu,GanShujian,ZhaoChao,WangPeiyang,MengChao,WangZhikui,HuMengjie(No.8511ResearchInstituteofCASIC,Nanjing210007,Jiangsu,China)Abstract:Inordertoachievegreaterpoweroutputinthemillimeterband,amillimeter-wavepower-combingtechnologyand3Dstackedpackageareproposed.BasedontheMEMSmachiningplatform,asubstrateintegrat-edwaveguidepowerdividerbasedonsiliconisdesigned,whichachieves20wattsofpower-combingat33~37GHz.Thepowerdividerandpoweramplifierarestackedandpackagedin3Dbywaferbondingtechnologytorealizeminiaturizationandhighdensityintegration.Thefeasibilityofhighpower-combingand3Dstackedpack-ageinthemillimeterbandareverifiedbyexperiments.Keywords:millimeter-wave;3Dstacked;substrateintegratedwaveguide;power-combing;waferbonding0引言毫米波技术在通信和雷达领域应用越来越广泛,但毫米波源较低的输出功率制约了其发展,将多个毫米波信号进行功率合成的技术是提高功率的有效技术途径。功率合成技术发展至今,通常采用Lange电桥[1]和功分器2种器件实现。Lange电桥的尺寸和频率相关,毫米波段的Lange桥尺寸小,需增加过渡微带才能与放大器芯片端口匹配,增加了装配的难度,导致传输损耗和端口驻波恶化。功分器的形式有很多种,其中基片集成波导[2](SIW)形式的功分器较为适合平面集成、大功率合成和毫米波频段的应用。但是传统的SIW功分器以PCB工艺平台为主,大多采用微波介质板或环氧树脂介质为基板,尺寸较大,加工精度较低,不易与功率放大器芯片进行小型化集成。微机电系统[3](MEMS)作为目前...