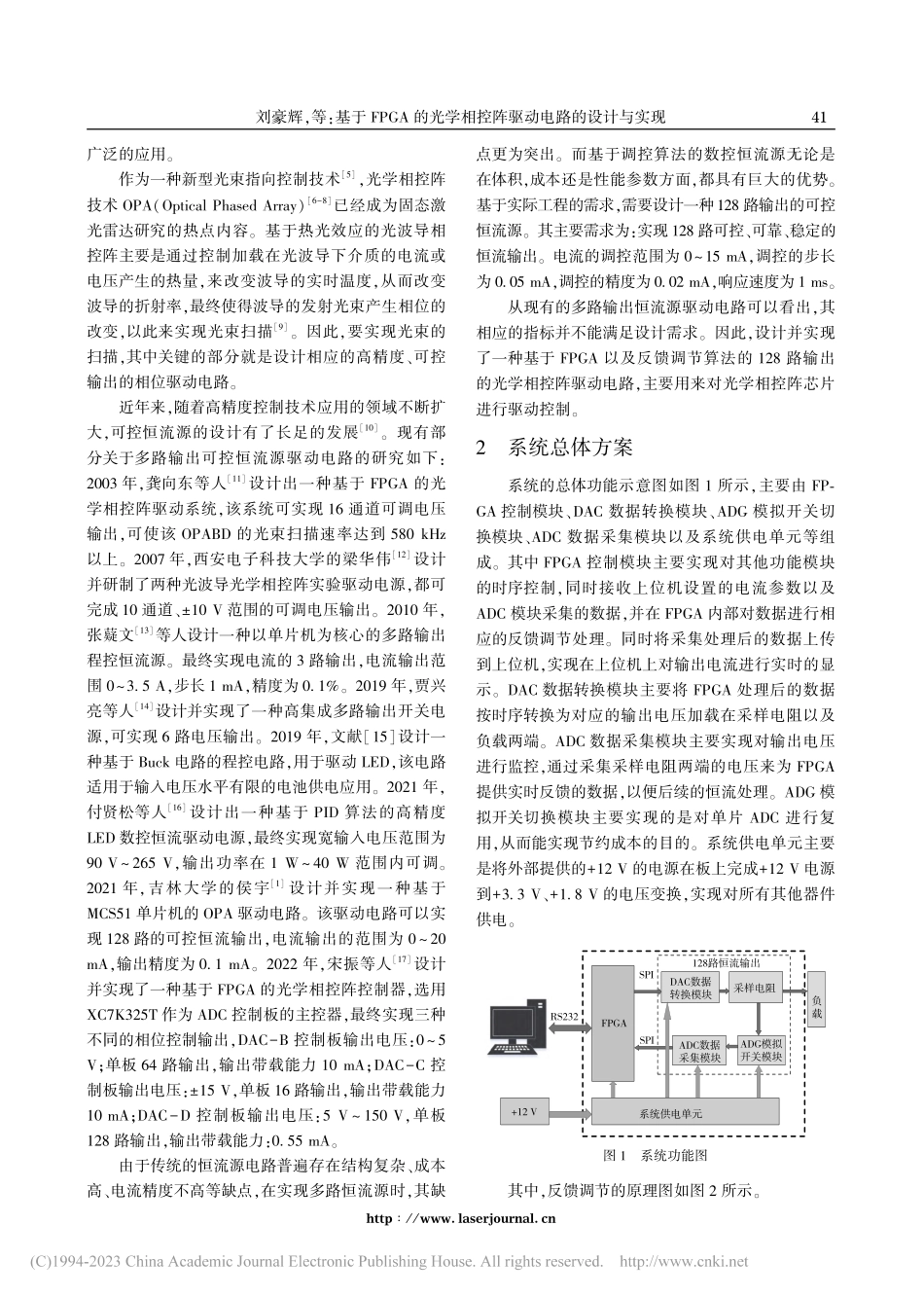

第44卷第4期2023年4月激光杂志LASERJOURNALVol.44,No.4April,2023http∶//www.laserjournal.cn收稿日期:2022-10-16基金项目:国家自然科学基金(No.62101204)作者简介:刘豪辉(1995-),男,硕士研究生,主要研究方向:嵌入式研究与应用。E-mail:Liuhh@mails.ccnu.edu.cn通讯作者:张青林(1983-),男,博士,副教授,硕士生导师,主要研究方向:图像处理、EDA技术、嵌入式系统。E-mail:93347858@qq.com·激光物理与器件·基于FPGA的光学相控阵驱动电路的设计与实现刘豪辉1,陆远2,王波1,刘建锋2,张青林11华中师范大学物理科学与技术学院,武汉430079;2上海航天电子技术研究所,上海201109摘要:传统的恒流源电路通常存在电路结构复杂、成本高等问题,满足不了一些高精度的应用要求。因此,结合实际工程的需要,设计并实现了一种基于现场可编程逻辑门阵列(FPGA)以及反馈调节算法的恒流源驱动电路,主要用于光学相控阵的相控单元控制。整个电路主要由FPGA控制模块、DAC模块、ADC模块、ADG模块以及采样电阻组成。通过FPGA接收调控参数,控制DAC模块进行输出,同时ADC模块对输出进行采集,在FPGA内对采集的数据进行反馈调控,最终实现128通道的可控恒流输出。电流的调控范围为0~15mA,调控的步长为0.05mA,调控的精度可达0.02mA,响应速度为1ms。系统的性能测试数据表明:基于FPGA的光学相控阵驱动电路具有响应速度快、电流输出精度高的优点,可满足对光学相控阵相位驱动的要求。关键词:光学相控阵;多路输出;驱动电路;电流源中图分类号:TN952文献标识码:Adoi:10.14016/j.cnki.jgzz.2023.04.040DesignandimplementationofopticalphasedarraydrivercircuitbasedonFPGALIUHaohui1,LUYuan2,WANGBo1,LIUJianfeng2,ZHANGQinglin11SchoolofPhysicalScienceandTechnology,CentralChinaNormalUniversity,Wuhan430079,China2ShanghaiInstituteofAerospaceElectronicsTechnology,Shanghai201109,ChinaAbstract:Thetraditionalconstantcurrentsourcecircuitusuallyhastheproblemsofcomplexcircuitstructureandhighcost,whichcannotmeettheapplicationrequirementsofsomehighprecision.Therefore,combinedwiththeneedsofpracticalengineering,thispaperdesignsandimplementsaconstantcurrentsourcedrivercircuitbasedonFP-GAandfeedbackregulationalgorithm,whichismainlyusedforthephasedunitcontrolofopticalphasedarray.ThewholecircuitismainlycomposedofFPGAcontrolmodule,DACmodule,ADCmodule,A...