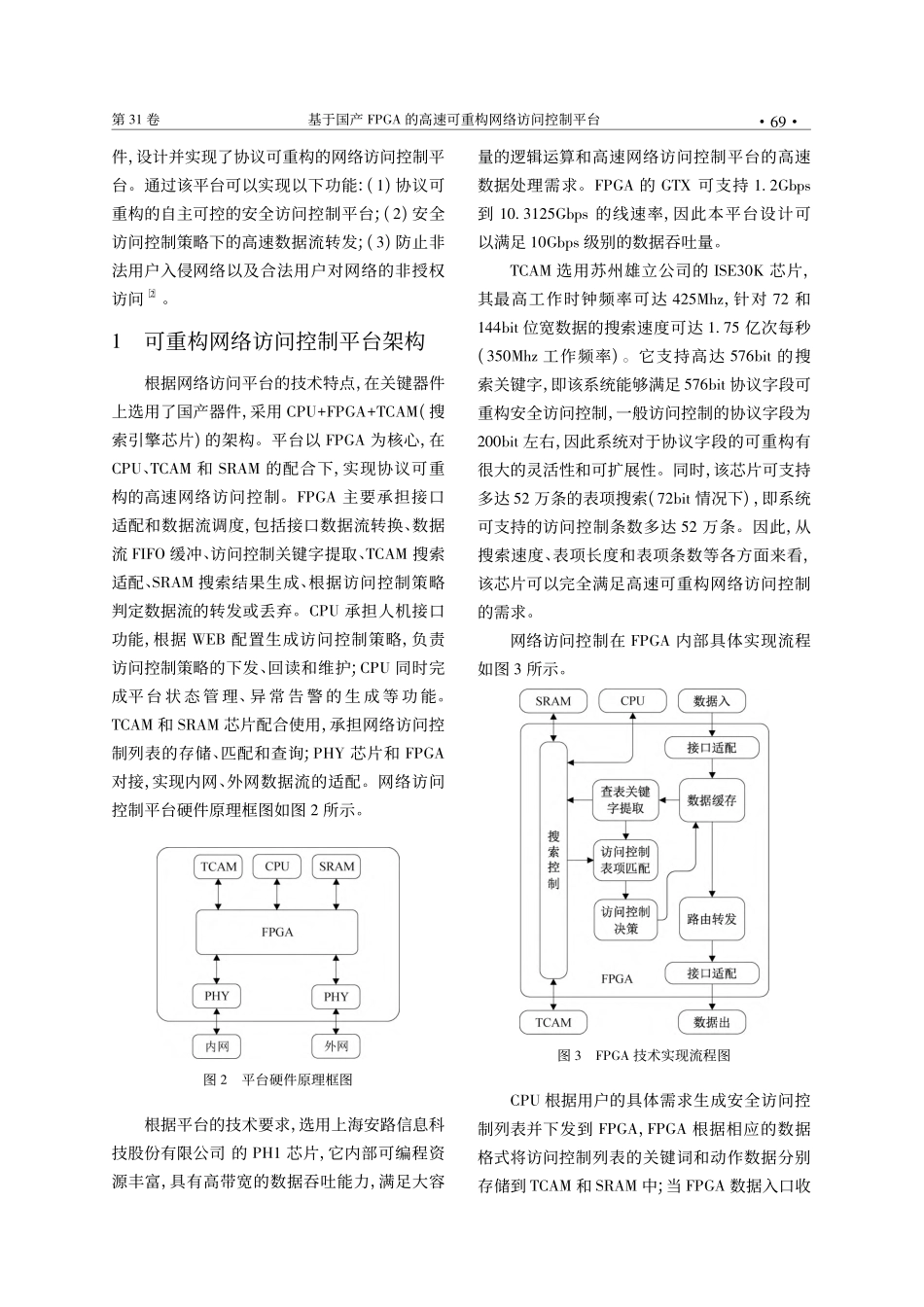

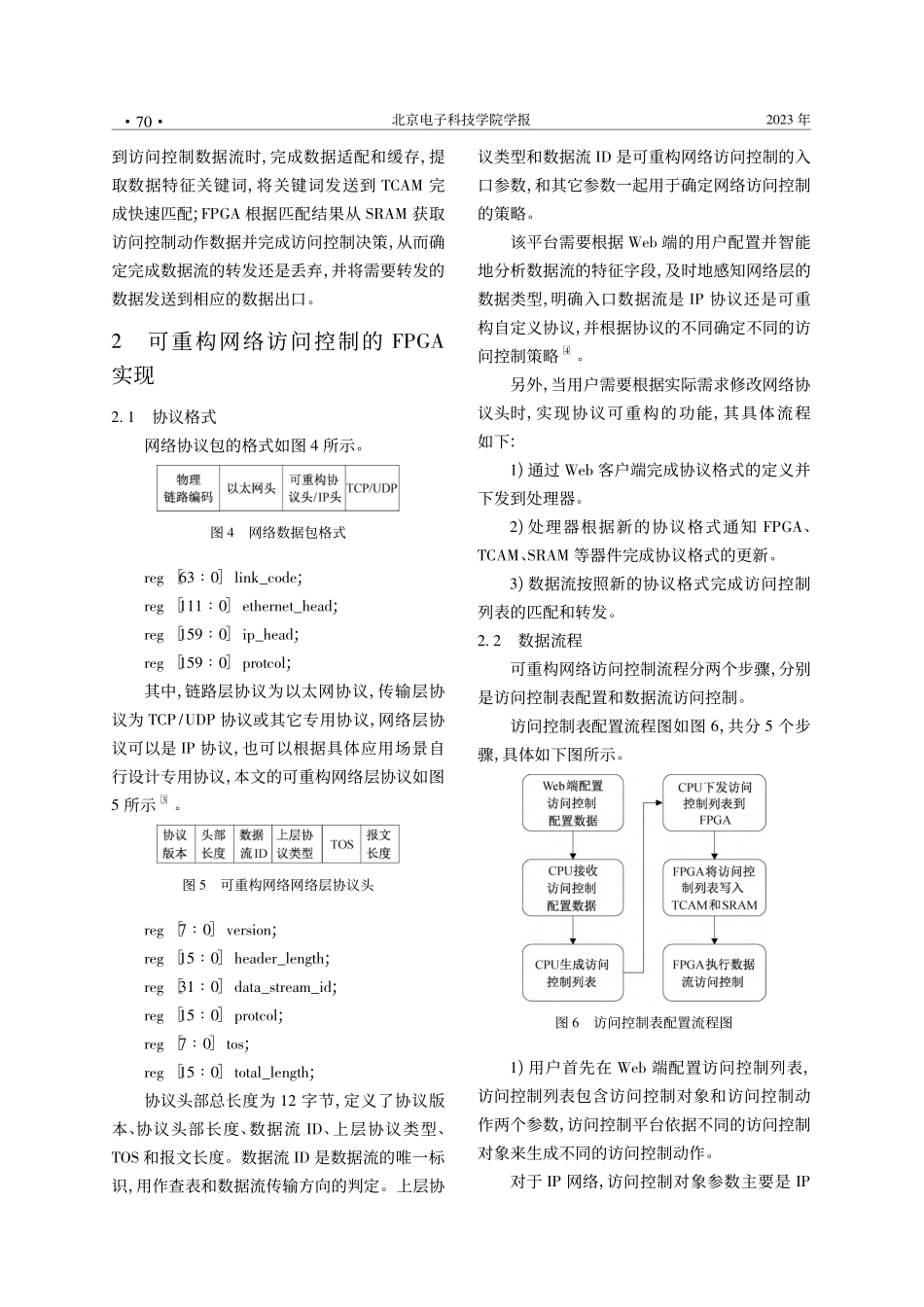

第31卷第1期北京电子科技学院学报2023年3月Vol.31No.1JournalofBeijingElectronicScienceandTechnologyInstituteMar.2023基于国产FPGA的高速可重构网络访问控制平台贾永兴吴捷陈明中国电子科技集团公司第三十研究所,成都市610041摘要:工业控制、电力通信等特殊行业对网络安全和自主可控提出了更多的需求,基于国产FPGA器件,提出了一种高速可重构的网络访问控制平台,给出了平台的技术架构、协议结构、数据业务流程等具体实现方法,并分析了平台的技术特点和优势。平台拥有协议可重构和高转发速率的优点,数据吞吐量可达10Gbps。该设计方法对自主可控的协议可重构的通信网络的具体实现具有很强的指导作用。关键词:国产FPGA;网络访问控制;可重构中图分类号:TP393.08文献标识码:A文章编号:1672-464X(2023)1-68-73*作者简介:贾永兴(1982-),男,高级工程师,主要研究方向为网络通信技术。吴捷(1981-),男,高级工程师,主要研究方向为网络通信技术。陈明(1987-),男,高级工程师,主要研究方向为网络通信技术。E-mail:jyxstar@126.com0引言随着互联网的快速发展和应用,在给人们日常办公和生活带来了极大方便的同时,网络安全问题也日益突出并倍受关注。网络访问控制技术作为网络安全的核心技术之一,通过在局域网内部实施准入准出规则,限制局域网内主机的访问权限,从而保证局域网资源受控地、合法地使用[1]。在边界路由器、入侵检测系统和防火墙等设备中通常都部署了网络访问控制技术和相关功能选项。工业控制、电力通信等特殊行业等典型局域网络对网络的自主可控和安全保密都有很高的要求,这些场景下需要采用安全可靠的网络安全设备去构建专用的高速保密通信网络,其网络层协议根据各自场景要求也不甚相同,会根据行业特点定制私有的协议。本文针对这类需求场景,提出了一种新型的高速可重构网络访问控制平台,其应用环境如图1所示。图1网络访问控制平台应用环境目前,针对IP协议网络访问控制技术已经很成熟了,但是针对自定义三层协议(非IP协议)的高速网络访问控制鲜有提及,首先,网络设备媒体介质层以上的协议层需要根据具体应用需求进行灵活定制,要求具备可重构的属性,不能通过通用芯片实现针对自定义协议特征的数据流访问控制;其次,因为通用处理器的程序指令、数据读写操作的架构设计带来的时延,通过处理器实现针对可重构的自定义协议特征的数据流访问控制无法满足高速转发性能要求。同时,中美贸易战愈演愈烈,集成电路“...