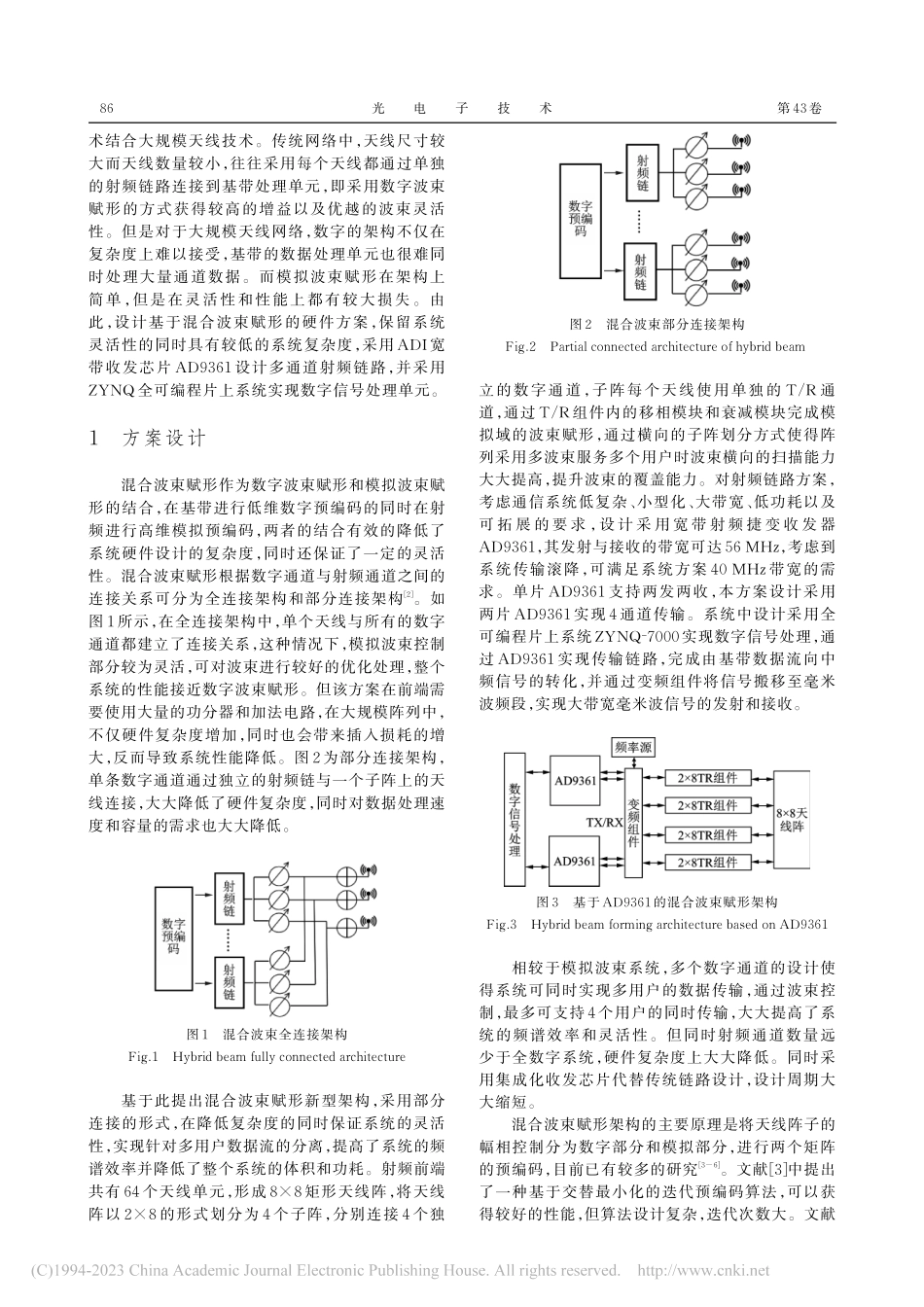

第43卷第1期2023年3月光电子技术OPTOELECTRONICTECHNOLOGYVol.43No.1Mar.2023基于混合波束赋形架构的数字中频系统方案设计毕鹏1∗,周骏2,包宽2(1.南京电子器件研究所,南京210016;2.南京国博电子股份有限公司,南京211111)摘要:对基于混合波束赋形的系统架构进行了研究。提出了新型的混合波束赋形架构,并采用高集成宽带收发芯片AD9361与全可编程片上系统进行多通道数字中频系统的搭建。测试结果表明该方案稳定可靠,满足大带宽高速传输的需求。关键词:混合波束赋形;宽带收发芯片;全可编程片上系统中图分类号:TN929.5文献标志码:A文章编号:1005⁃488X(2023)01⁃0085⁃05DesignofDigitalIFSystemBasedonHybridBeamFormingArchitectureBIPeng,ZHOUJun,BAOKuan(1.NanjingElectronicDevicesInstitute,Nanjing210016;2.NanjingGuoboElectronicsCo.,LTD,Nanjing211111)Abstract:Thesystemarchitecturebasedonhybridbeamformingwasstudied,anewhybridbeamformingarchitecturewasproposed,andhighlyintegratedbroadbandtransceiverchipAD9361andallprogrammableSoCwasusedtobuildamulti-channeldigitalintermediatefrequencysystem.Thetestresultsshowedthattheschemewasstableandreliable,andcouldmeetthedemandsoflargebandwidthandhighspeedtransmission.Keywords:hybridbeamforming;broadbandtransceiverchip;allprogrammableSoC引言随着新一代通信技术的推进,5G网络针对连接密度、通信速率和延时性提出了较大的提升要求。为了满足5G网络爆炸性数据增长和巨大的连接密度,需要在通信系统和传输技术上进行研究和提升[1]。由香农定理可知,提升系统容量主要有三个方向:1)增加带宽;目前低频段频谱资源难以满足5G的大带宽需求,5G的潜力在毫米波高频段。2)增加网络覆盖;通过超密集组网的方式可以充分利用频谱资源,但是也对通信设备提出了低功耗、小型化的要求。3)提升频谱效率;高阶调制技术和复用技术是4G网络提升频谱效率的有效手段,但是5G获得较大频谱效率提升的关键在于波束赋形技DOI:10.19453/j.cnki.1005⁃488x.2023.01.014收稿日期:2023-02-05作者简介:毕鹏(1999—),男,硕士研究生,主要研究方向:混合波束赋形技术,嵌入式系统;(Email:3014473228@qq.com)包宽(1987—),男,博士,高级工程师,主要研究方向:微波毫米波射频前端领域新技术以及新应用研究;周骏(1982—),男,博士,研究员级高工,主要...