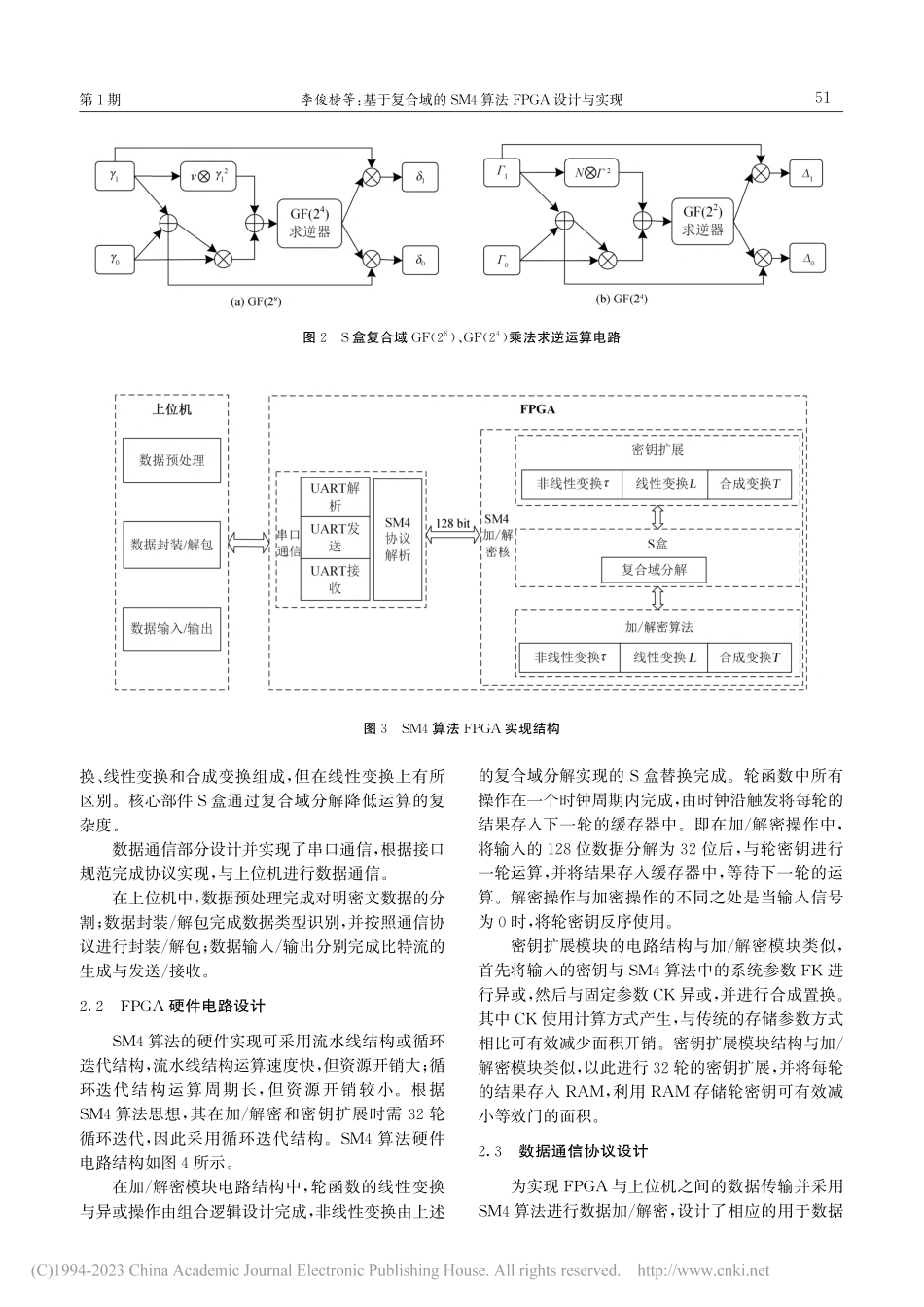

第43卷第1期桂林电子科技大学学报Vol.43,No.12023年2月JournalofGuilinUniversityofElectronicTechnologyFeb.2023收稿日期:2021-04-28基金项目:广西青年创新人才科研专项(桂科AD20238082);广西大学生创新训练计划(202010595195,202010595138).通信作者:张润莲(1974-),女,副教授,博士,研究方向为信息安全和分布式计算.E-mail:zhangrl@guet.edu.cn引文格式:李俊榜,李金林,潘晟,等.基于复合域的SM4算法FPGA设计与实现[J].桂林电子科技大学学报,2023,43(1):49-55.基于复合域的SM4算法FPGA设计与实现李俊榜,李金林,潘晟,梁家任,钟雪绮,张润莲(桂林电子科技大学广西密码学与信息安全重点实验室,广西桂林541004)摘要:推广和应用国密算法是加强我国信息安全的重要举措。提高密码算法的实现速度,降低其硬件实现成本,已成为实际应用中的迫切需求。该问题的解决方案之一是基于复合域的SM4算法FPGA硬件设计与实现。基于对S盒的复合域分解和电路优化,该方案降低了硬件逻辑门数;同时重构基于复合域的SM4算法硬件电路,并改进了轮常量和轮密钥的生成和存储方式,以降低硬件面积;设计了数据通信模式,以实现上位机和FPGA之间的通信,并通过数据加解密为应用提供安全支持。仿真测试和软硬件实现证实了基于复合域的SM4算法FPGA硬件实现的正确性,同时提高了算法的吞吐量。综合评测结果表明,该方案具有更小的实现面积。关键词:SM4;S盒;复合域;仿射变换;FPGA中图分类号:TP393文献标志码:A文章编号:1673-808X(2023)01-0049-07TheFPGAdesignandimplementationofSM4basedoncompositefieldLIJunbang,LIJinlin,PANSheng,LIANGJiaren,ZHONGXueqi,ZHANGRunlian(GuangxiKeyLaboratoryofCryptographyandInformationSecurity,GuilinUniversityofElectronicTechnology,Guilin541004,China)Abstract:ThepromotionandapplicationoftheSM(CommercialCryptography)algorithmisanimportantmeasureforstrengtheninginformationsecurityinChina.Increasingthespeedofimplementingencryptionalgorithmsandreducingthehardwareimplementationcostshavebecomeurgentneedsinpracticalapplications.OnesolutiontothisproblemistheFPGAhardwaredesignandimplementationoftheSM4algorithmbasedoncompositefields.ThesolutionreducesthenumberofhardwarelogicgatesbyusingthecompositefielddecompositionoftheS-boxandcircuitoptimization.Inaddition,thehard-warecircuitoftheSM4algorithmbasedoncompo...