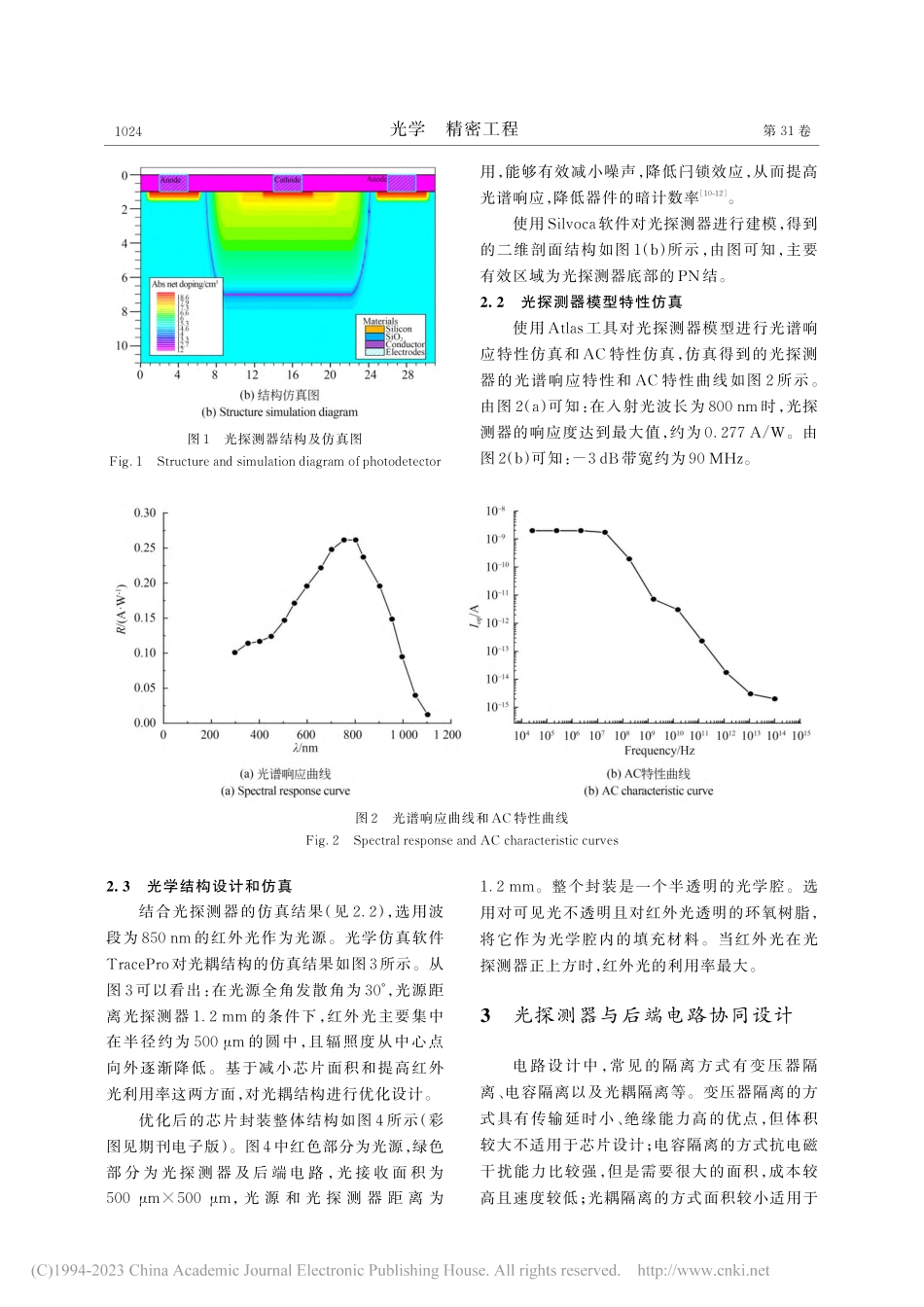

第31卷第7期2023年4月Vol.31No.7Apr.2023光学精密工程OpticsandPrecisionEngineering单片集成光耦隔离式驱动芯片程翔1,常浩然1,刘岩2*,邓晨洋1,严旭杰1(1.厦门大学航空航天学院,福建厦门361104;2.集美大学海洋信息工程学院,福建厦门361021)摘要:在功率半导体市场中,绝缘栅双极型晶体管(Insulatedgatebipolartransistor,IGBT)和碳化硅金属氧化物半导体场效应管(Siliconcarbidemetal-oxide-semiconductorfield-effecttransistor,SiCMOSFET)具有出色的耐压性与频率特性,逐渐取代了传统的MOSFET。为了提高IGBT和SiCMOSFET驱动电路的可靠性,设计了一款光耦隔离式栅极驱动芯片,通过协同设计光探测器与驱动电路,从而实现单片集成。使用Silvaco软件对光探测器进行了仿真。仿真结果显示:光探测器对800nm波长红外光的响应度约为0.277A/W,-3dB带宽约为90MHz。进一步对光耦的光学结构进行优化设计,实现了控制端与后端高压驱动电路的有效隔离,从而解决了串扰问题。使用Maxchip0.18μm40VBCD工艺进行流片,并对封装芯片进行测试。在光源输入电流为10mA、芯片供电电压为12~40V、输入信号频率为20kHz的测试条件下,芯片的传播延时仅为98ns。关键词:协同设计;单片集成;光耦隔离;低延时中图分类号:TN312文献标识码:Adoi:10.37188/OPE.20233107.1022MonolithicoptocouplerisolateddriverchipCHENGXiang1,CHANGHaoran1,LIUYan2*,DENGChenyang1,YANXujie1(1.SchoolofAerospaceEngineering,XiamenUniversity,Xiamen361104,China;2.SchoolofMarineInformationEngineering,JimeiUniversity,Xiamen361021,China)*Correspondingauthor,E-mail:ly_liu@jmu.edu.cnAbstract:Inthepowersemiconductormarket,insulatedgatebipolartransistor(IGBT)andsiliconcar⁃bidemetal-oxide-semiconductorfield-effecttransistors(SiCMOSFETs)haveexcellentvoltageresistanceandfrequencycharacteristics,andthusgraduallyreplacedthetraditionalMOSFETs.Thereliabilityde⁃signofIGBTandSiCMOSFETdrivercircuitsisassociatedwithrigorouschallenges.Therefore,anopto⁃coupler-isolatedgatedriverchipwasdesignedinthisstudy.Monolithicintegrationwasrealizedbyco-de⁃signingphotodetectorsanddrivercircuits.Silveracosoftwarewasusedtosimulatethephotodetector.Thesimulationresultsindicatethattheresponsivityofthephotodete...