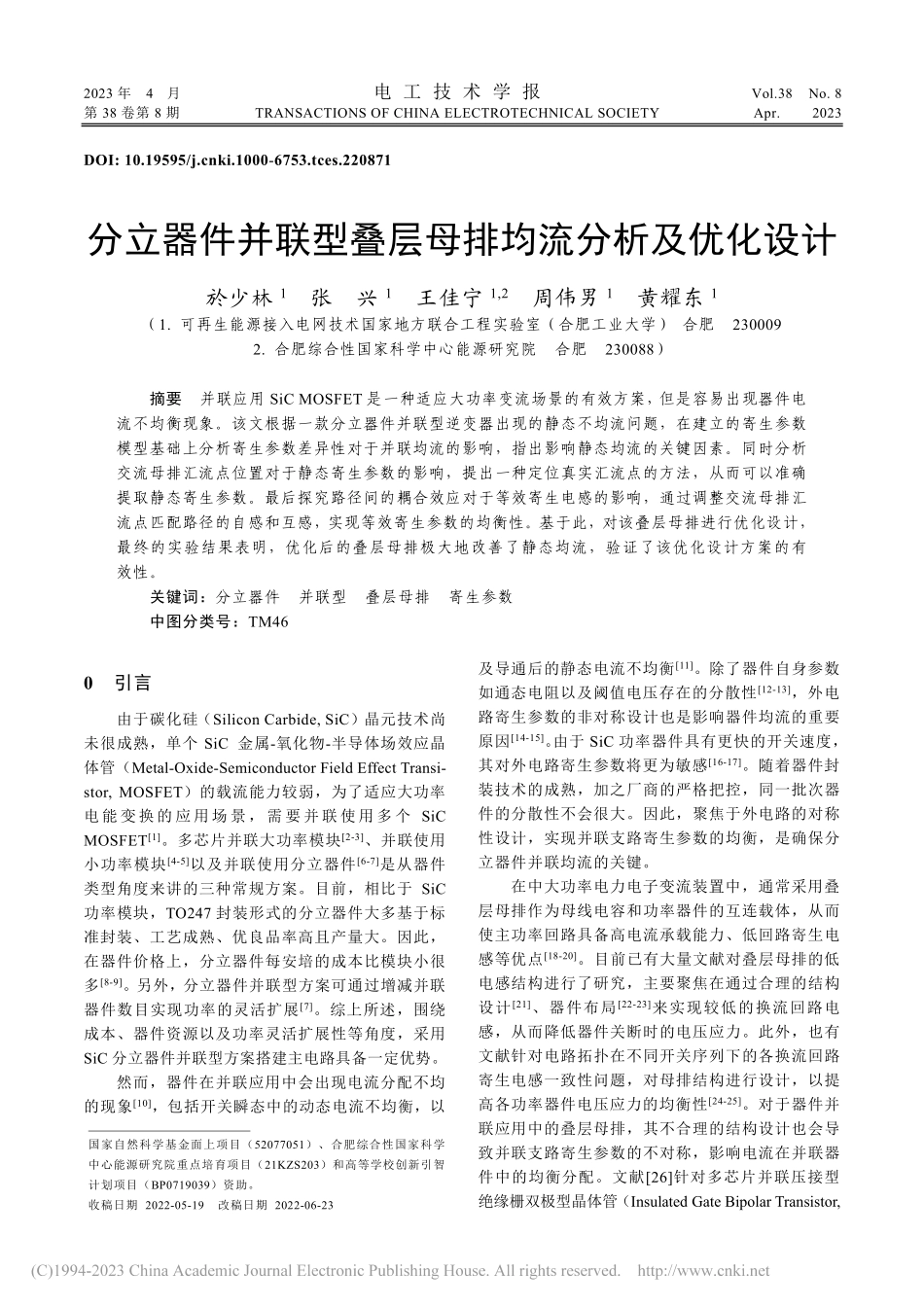

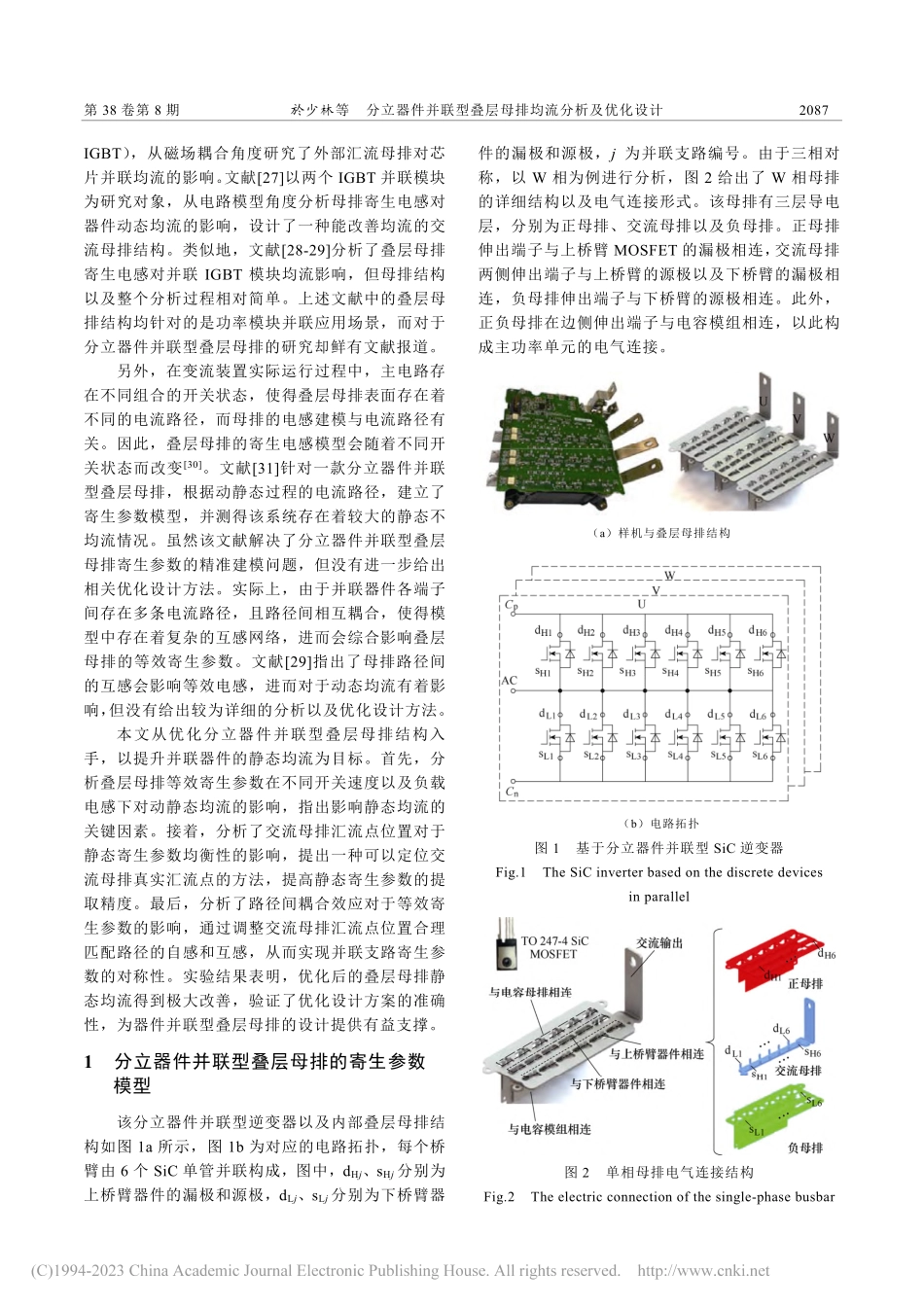

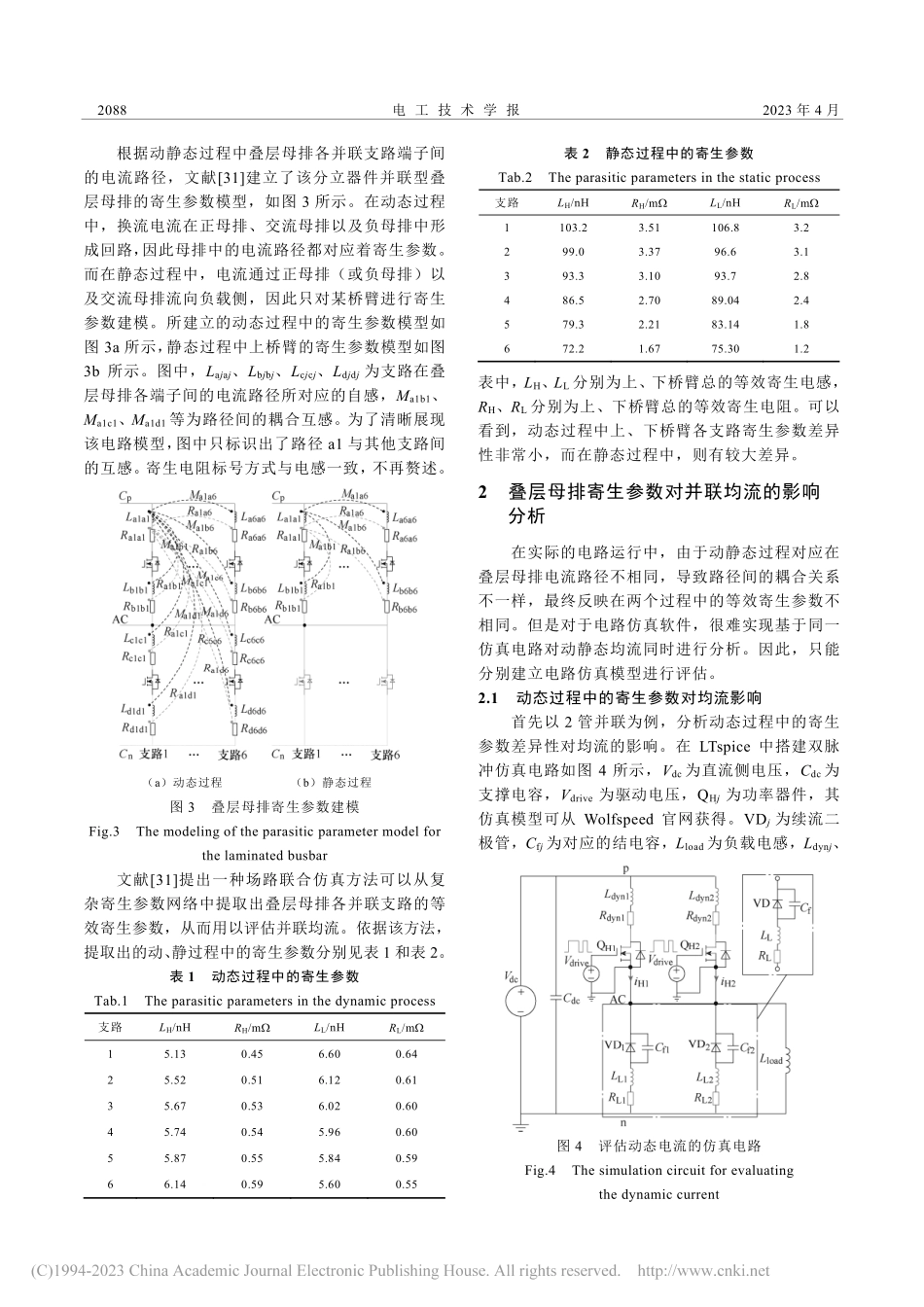

2023年4月电工技术学报Vol.38No.8第38卷第8期TRANSACTIONSOFCHINAELECTROTECHNICALSOCIETYApr.2023DOI:10.19595/j.cnki.1000-6753.tces.220871分立器件并联型叠层母排均流分析及优化设计於少林1张兴1王佳宁1,2周伟男1黄耀东1(1.可再生能源接入电网技术国家地方联合工程实验室(合肥工业大学)合肥2300092.合肥综合性国家科学中心能源研究院合肥230088)摘要并联应用SiCMOSFET是一种适应大功率变流场景的有效方案,但是容易出现器件电流不均衡现象。该文根据一款分立器件并联型逆变器出现的静态不均流问题,在建立的寄生参数模型基础上分析寄生参数差异性对于并联均流的影响,指出影响静态均流的关键因素。同时分析交流母排汇流点位置对于静态寄生参数的影响,提出一种定位真实汇流点的方法,从而可以准确提取静态寄生参数。最后探究路径间的耦合效应对于等效寄生电感的影响,通过调整交流母排汇流点匹配路径的自感和互感,实现等效寄生参数的均衡性。基于此,对该叠层母排进行优化设计,最终的实验结果表明,优化后的叠层母排极大地改善了静态均流,验证了该优化设计方案的有效性。关键词:分立器件并联型叠层母排寄生参数中图分类号:TM460引言由于碳化硅(SiliconCarbide,SiC)晶元技术尚未很成熟,单个SiC金属-氧化物-半导体场效应晶体管(Metal-Oxide-SemiconductorFieldEffectTransi-stor,MOSFET)的载流能力较弱,为了适应大功率电能变换的应用场景,需要并联使用多个SiCMOSFET[1]。多芯片并联大功率模块[2-3]、并联使用小功率模块[4-5]以及并联使用分立器件[6-7]是从器件类型角度来讲的三种常规方案。目前,相比于SiC功率模块,TO247封装形式的分立器件大多基于标准封装、工艺成熟、优良品率高且产量大。因此,在器件价格上,分立器件每安培的成本比模块小很多[8-9]。另外,分立器件并联型方案可通过增减并联器件数目实现功率的灵活扩展[7]。综上所述,围绕成本、器件资源以及功率灵活扩展性等角度,采用SiC分立器件并联型方案搭建主电路具备一定优势。然而,器件在并联应用中会出现电流分配不均的现象[10],包括开关瞬态中的动态电流不均衡,以及导通后的静态电流不均衡[11]。除了器件自身参数如通态电阻以及阈值电压存在的分散性[12-13],外电路寄生参数的非对称设计也是影响器件均流的重要原因[14-15]。由于SiC功率器件具有更快的开关速度,其对外电路寄生参数将更为敏感[16-17]。随着器件封装技术的成熟,加之厂商的严格把控,同一批次...