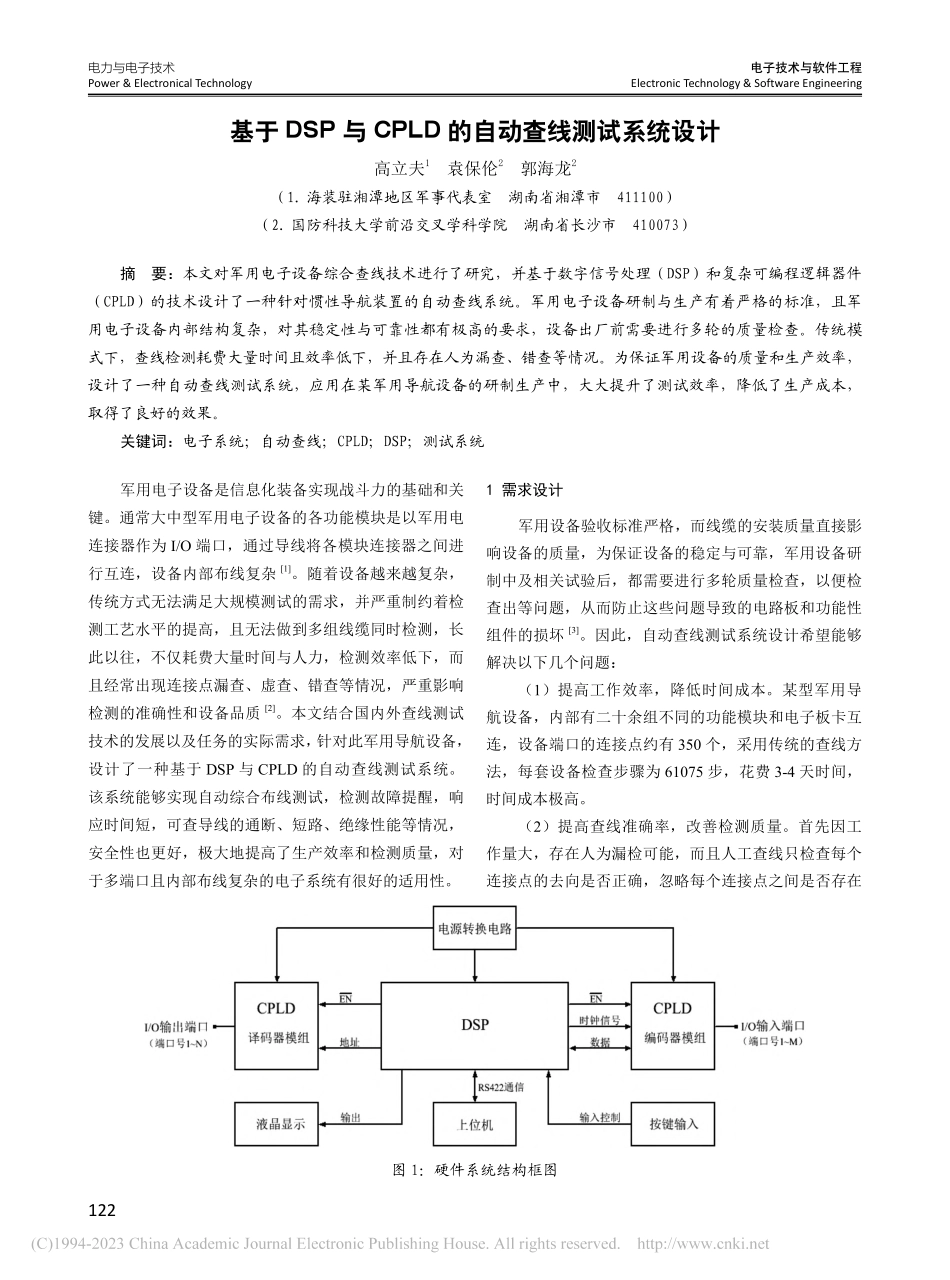

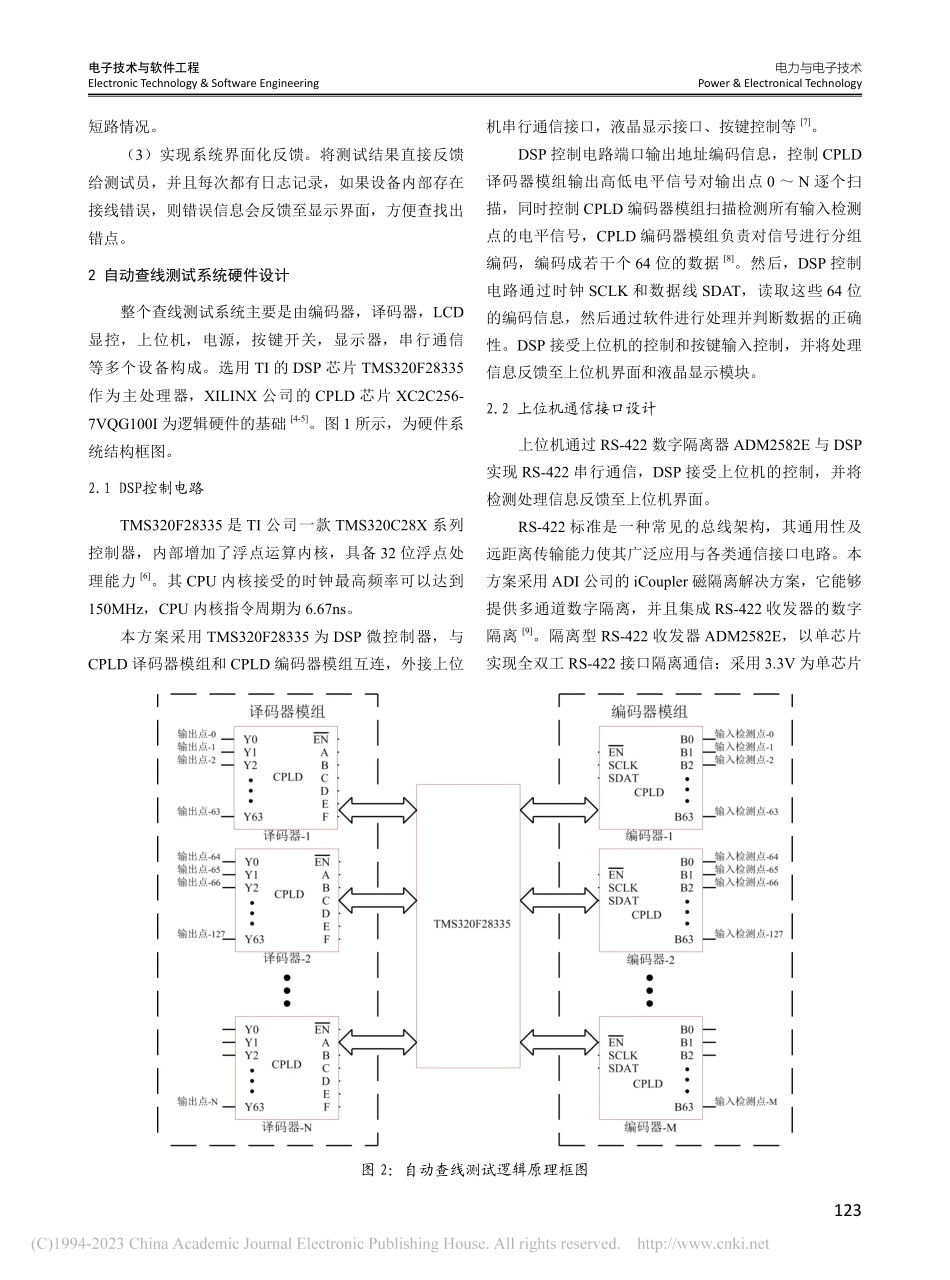

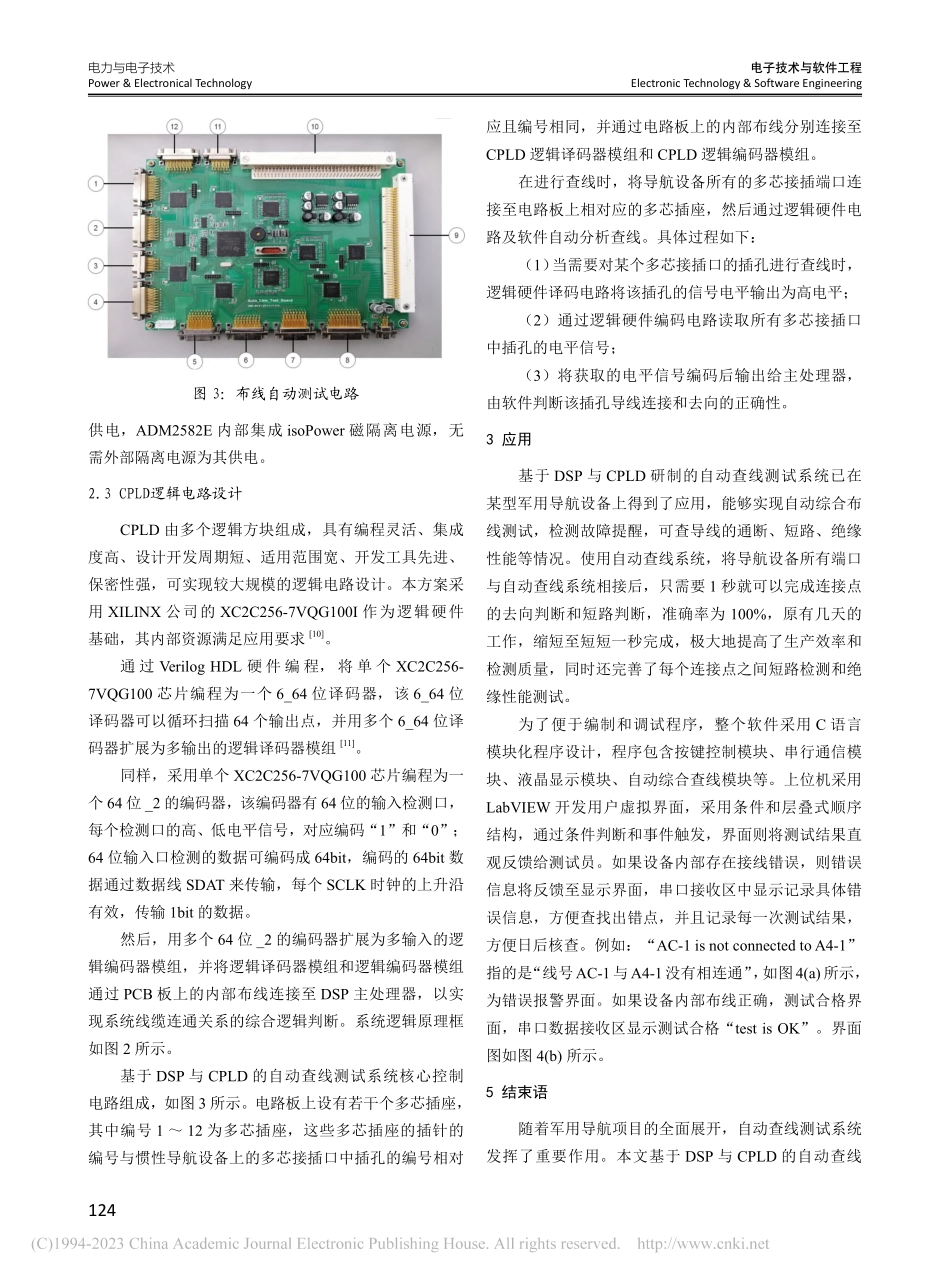

电力与电子技术Power&ElectronicalTechnology电子技术与软件工程ElectronicTechnology&SoftwareEngineering122军用电子设备是信息化装备实现战斗力的基础和关键。通常大中型军用电子设备的各功能模块是以军用电连接器作为I/O端口,通过导线将各模块连接器之间进行互连,设备内部布线复杂[1]。随着设备越来越复杂,传统方式无法满足大规模测试的需求,并严重制约着检测工艺水平的提高,且无法做到多组线缆同时检测,长此以往,不仅耗费大量时间与人力,检测效率低下,而且经常出现连接点漏查、虚查、错查等情况,严重影响检测的准确性和设备品质[2]。本文结合国内外查线测试技术的发展以及任务的实际需求,针对此军用导航设备,设计了一种基于DSP与CPLD的自动查线测试系统。该系统能够实现自动综合布线测试,检测故障提醒,响应时间短,可查导线的通断、短路、绝缘性能等情况,安全性也更好,极大地提高了生产效率和检测质量,对于多端口且内部布线复杂的电子系统有很好的适用性。1需求设计军用设备验收标准严格,而线缆的安装质量直接影响设备的质量,为保证设备的稳定与可靠,军用设备研制中及相关试验后,都需要进行多轮质量检查,以便检查出等问题,从而防止这些问题导致的电路板和功能性组件的损坏[3]。因此,自动查线测试系统设计希望能够解决以下几个问题:(1)提高工作效率,降低时间成本。某型军用导航设备,内部有二十余组不同的功能模块和电子板卡互连,设备端口的连接点约有350个,采用传统的查线方法,每套设备检查步骤为61075步,花费3-4天时间,时间成本极高。(2)提高查线准确率,改善检测质量。首先因工作量大,存在人为漏检可能,而且人工查线只检查每个连接点的去向是否正确,忽略每个连接点之间是否存在基于DSP与CPLD的自动查线测试系统设计高立夫1袁保伦2郭海龙2(1.海装驻湘潭地区军事代表室湖南省湘潭市411100)(2.国防科技大学前沿交叉学科学院湖南省长沙市410073)摘要:本文对军用电子设备综合查线技术进行了研究,并基于数字信号处理(DSP)和复杂可编程逻辑器件(CPLD)的技术设计了一种针对惯性导航装置的自动查线系统。军用电子设备研制与生产有着严格的标准,且军用电子设备内部结构复杂,对其稳定性与可靠性都有极高的要求,设备出厂前需要进行多轮的质量检查。传统模式下,查线检测耗费大量时间且效率低下,并且存在人为漏查、错查等情况。为保证军用设备的质量和生产效率,设计了一种自动查线测试系统,应用在...