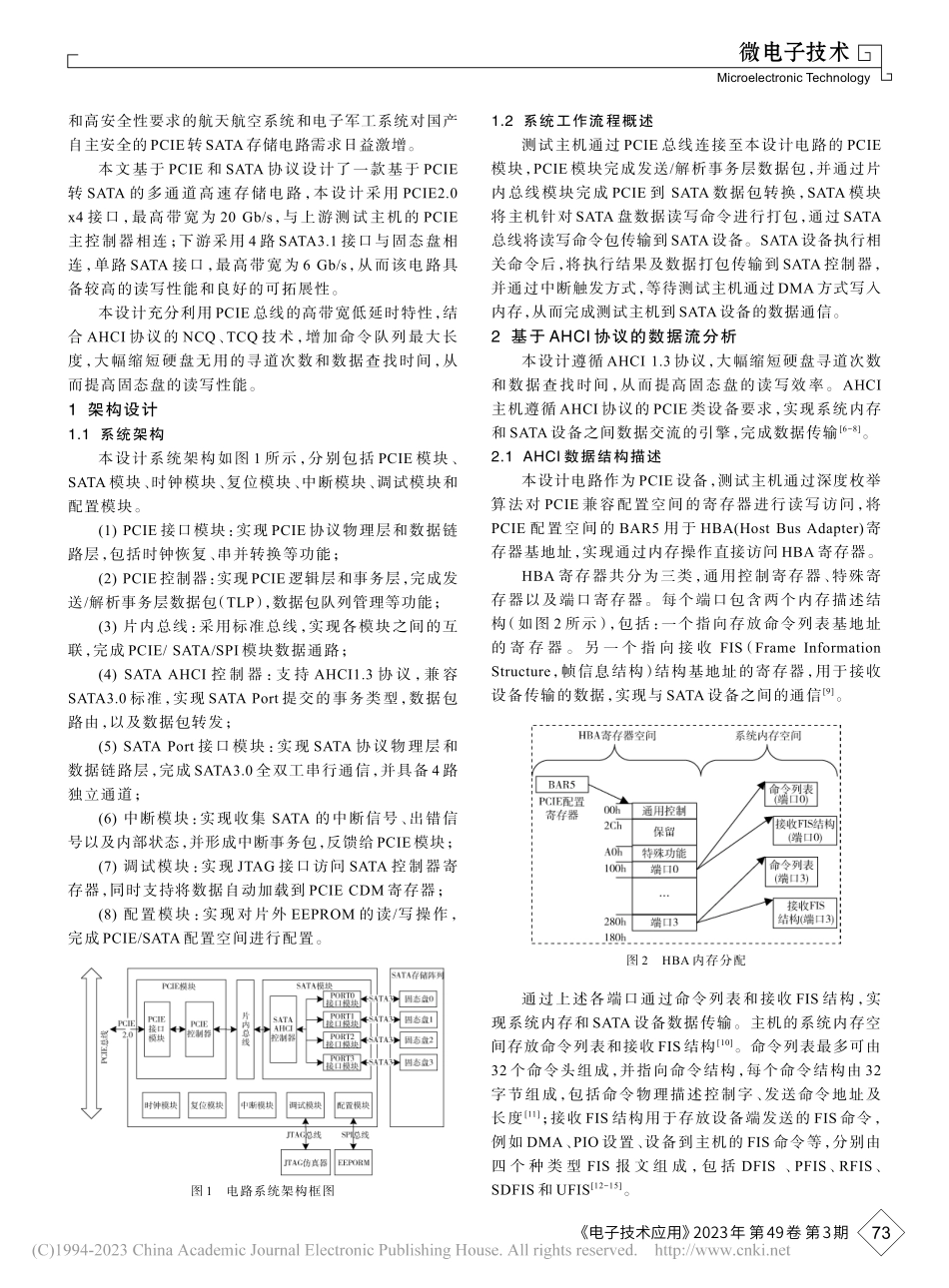

www.ChinaAET.comMicroelectronicTechnology微电子技术基于PCIE转SATA多通道高速存储电路设计与原型验证王琪,张梅娟,邓佳伟,杨楚玮,周迁(中国电子科技集团公司第五十八研究所,江苏无锡214035)摘要:针对传统SATA控制器接口单一且无法充分发挥固态盘性能的问题,设计了一款基于PCIE转SATA多通道高速存储电路。充分利用PCIE总线高带宽低延时特性,并遵循AHCI协议,大幅缩短硬盘无用的寻道次数和数据查找时间,提高固态盘的读写性能,同时本设计可支持4路SATA通道,具有良好的可拓展性。设计结合PCIE和SATA协议特点,介绍了PCIE转SATA高速存储电路的系统架构,详细阐述了基于AHCI协议的数据流传输过程。最后基于FPGA原型验证对电路进行测试,电路的单盘读写速率分别为562MB/s和527MB/s,相比传统SATA控制器的读写性能具有较大提升,测试结果表明设计的PCIE转SATA高速存储电路读写性能优异,且具备良好的稳定性和可拓展性。关键词:PCIE转SATA;AHCI协议;多通道;FPGA验证中图分类号:TN401文献标志码:ADOI:10.16157/j.issn.0258-7998.223077中文引用格式:王琪,张梅娟,邓佳伟,等.基于PCIE转SATA多通道高速存储电路设计与原型验证[J].电子技术应用,2023,49(3):72-76.英文引用格式:WangQi,ZhangMeijuan,DengJiawei,etal.Designandprototypeverificationofmulti-channelhigh-speedstoragecircuitbaseonPCIEtoSATA[J].ApplicationofElectronicTechnique,2023,49(3):72-76.Designandprototypeverificationofmulti-channelhigh-speedstoragecircuitbaseonPCIEtoSATAWangQi,ZhangMeijuan,DengJiawei,YangChuwei,ZhouQian(ChinaElectronicsTechnologyGroupCorporationNo.58ResearchInstitute,Wuxi214035,China)Abstract:AimingattheproblemthatthetraditionalSATAcontrollerhasasingleinterfaceandcannotgivefullplaytotheper‐formanceoftheSSD,amulti-channelhigh-speedstoragecircuitbasedonPCIEtoSATAisdesigned.Thisdesignmakesfulluseofthehigh-bandwidthandlow-latencycharacteristicsofthePCIEbusandfollowstheAHCIprotocol,whichcangreatlyreducetheuselessseektimesanddatasearchtimeoftheharddisk,andimprovethereadperformance.Atthesametime,thedesigncansupport4SATAchannelsandhasgoodscalability.ThisdesigncombinesthecharacteristicsofPCIEandSATAprotocols,intro‐ducesthesystemarchitectureofPCIEtoSATAhig...