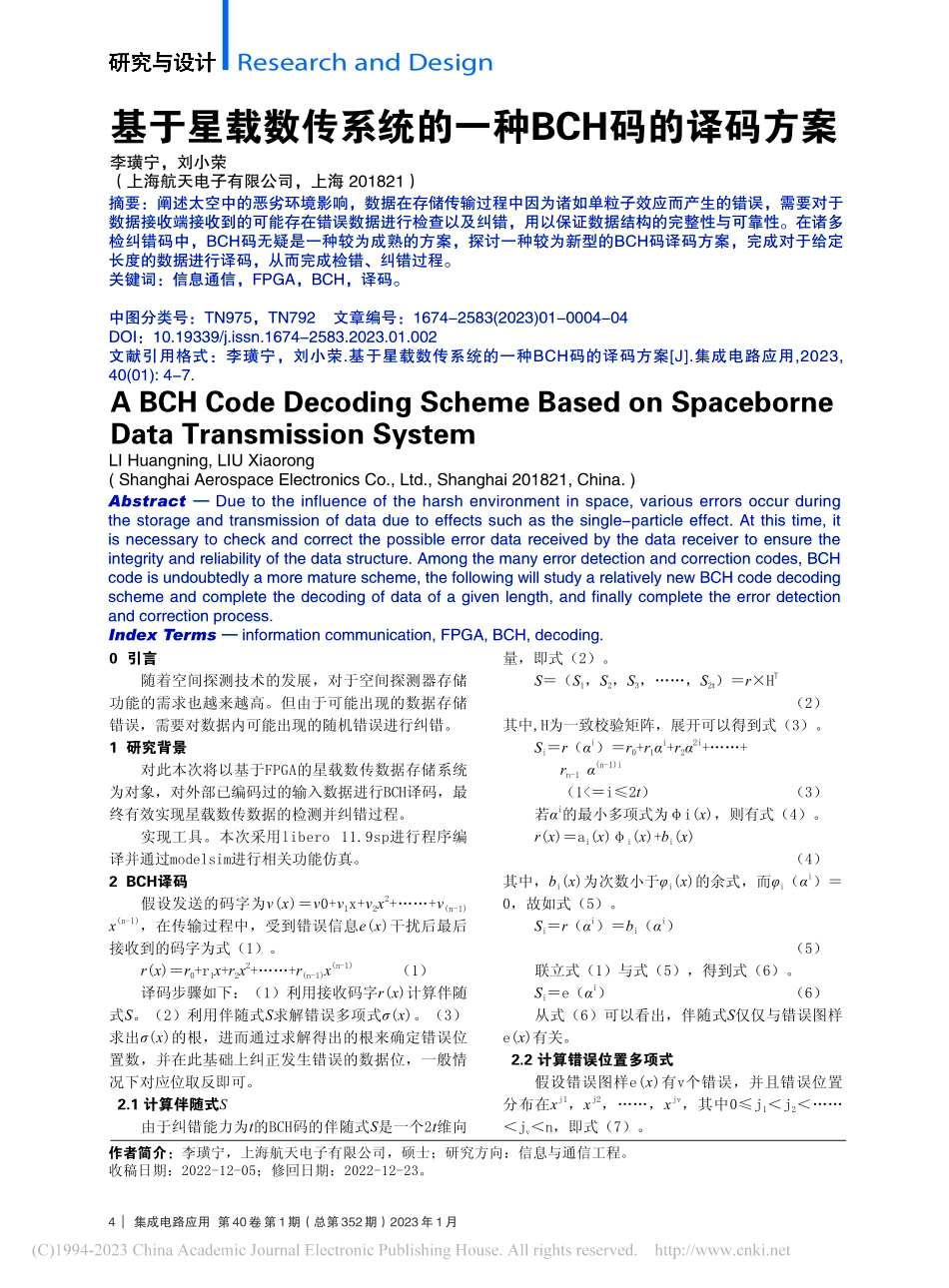

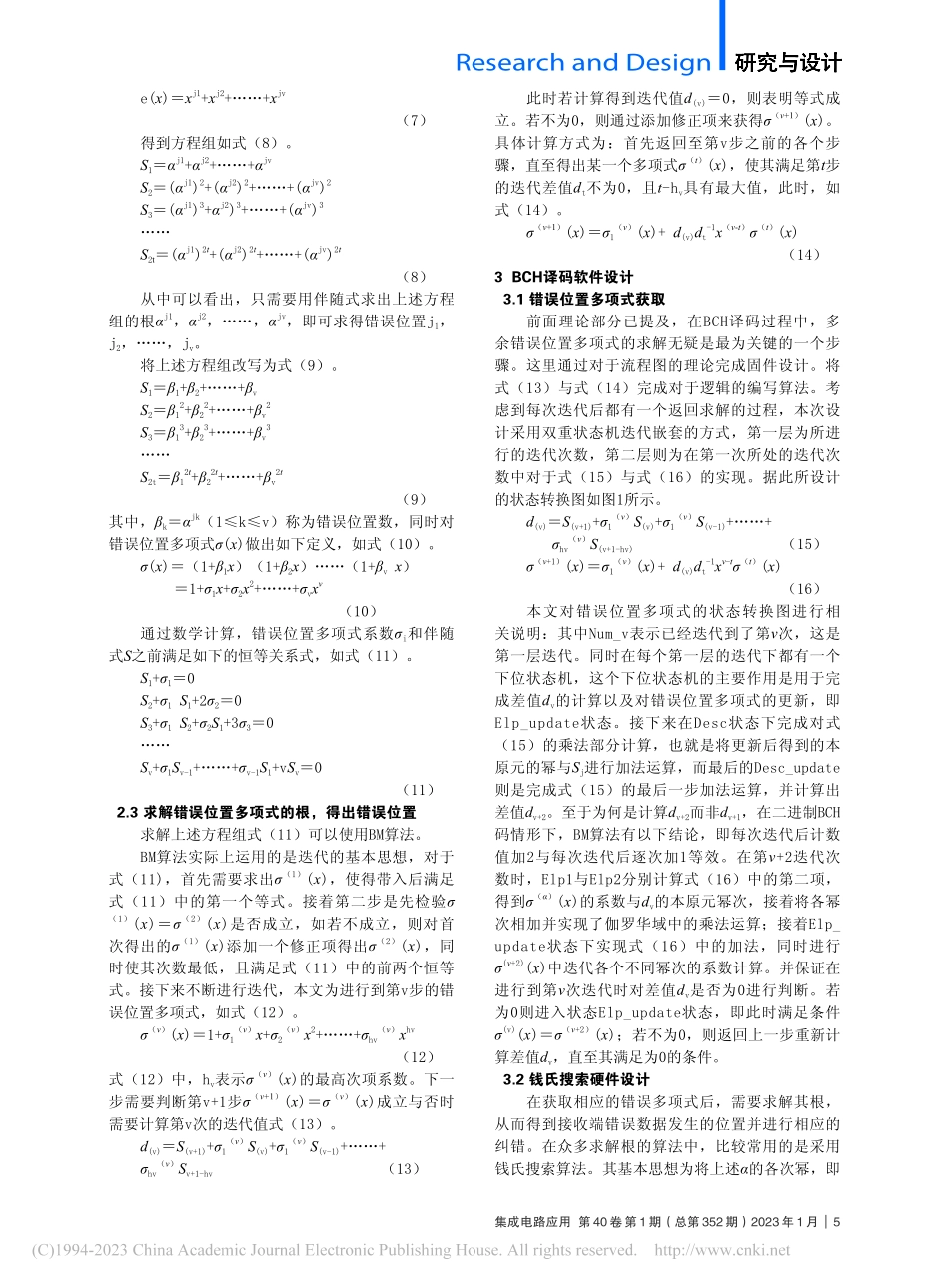

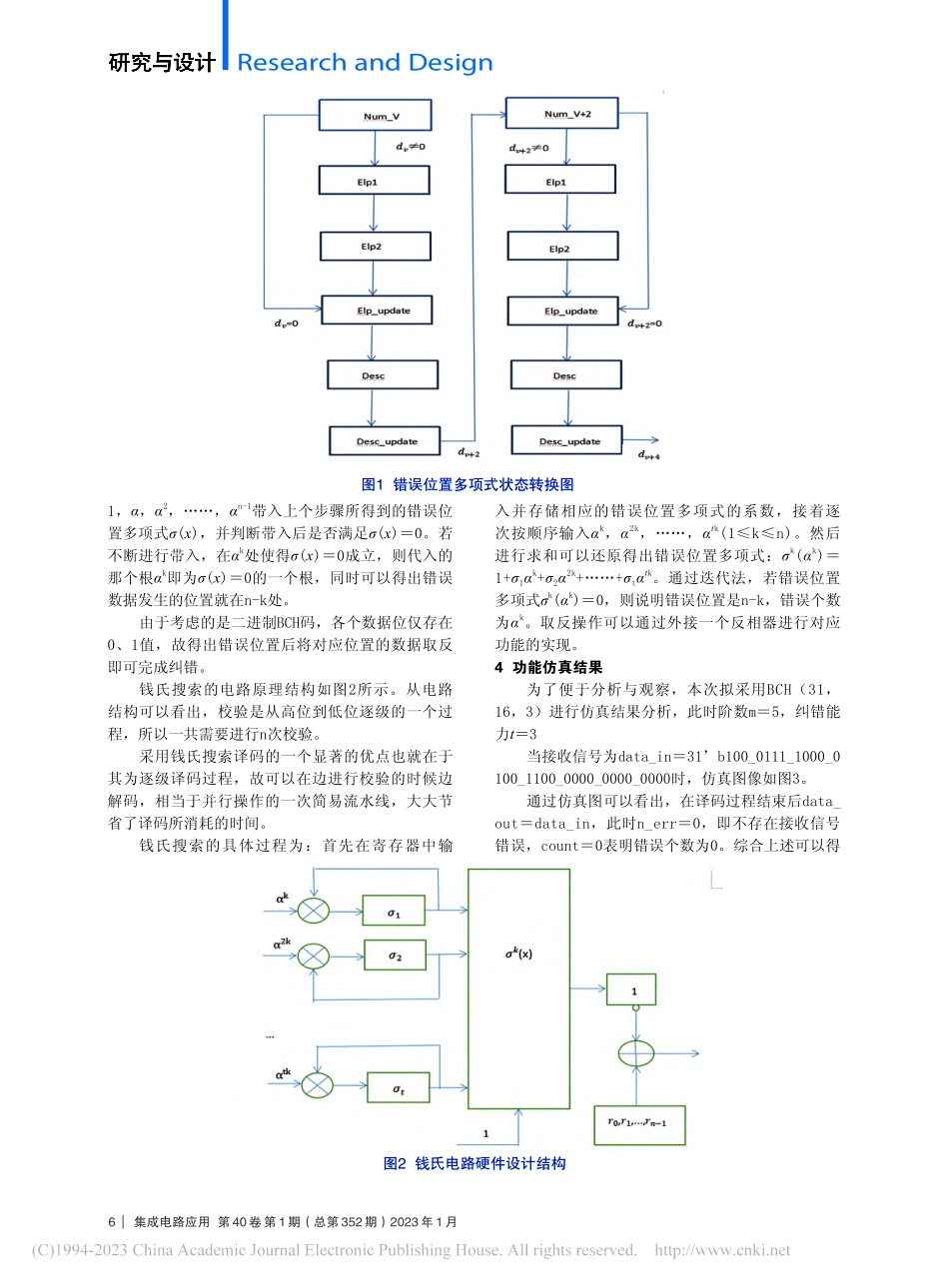

4集成电路应用第40卷第1期(总第352期)2023年1月ResearchandDesign研究与设计0引言随着空间探测技术的发展,对于空间探测器存储功能的需求也越来越高。但由于可能出现的数据存储错误,需要对数据内可能出现的随机错误进行纠错。1研究背景对此本次将以基于FPGA的星载数传数据存储系统为对象,对外部已编码过的输入数据进行BCH译码,最终有效实现星载数传数据的检测并纠错过程。实现工具。本次采用libero11.9sp进行程序编译并通过modelsim进行相关功能仿真。2BCH译码假设发送的码字为v(x)=v0+v1x+v2x2+……+v(n-1)x(n-1),在传输过程中,受到错误信息e(x)干扰后最后接收到的码字为式(1)。r(x)=r0+r1x+r2x2+……+r(n-1)x(n-1)(1)译码步骤如下:(1)利用接收码字r(x)计算伴随式S。(2)利用伴随式S求解错误多项式σ(x)。(3)求出σ(x)的根,进而通过求解得出的根来确定错误位置数,并在此基础上纠正发生错误的数据位,一般情况下对应位取反即可。2.1计算伴随式S由于纠错能力为t的BCH码的伴随式S是一个2t维向量,即式(2)。S=(S1,S2,S3,……,S2t)=r×HT(2)其中,H为一致校验矩阵,展开可以得到式(3)。Si=r(αi)=r0+r1αi+r2α2i+……+rn-1α(n-1)i(1<=i≤2t)(3)若αi的最小多项式为φi(x),则有式(4)。r(x)=ai(x)φi(x)+bi(x)(4)其中,bi(x)为次数小于φi(x)的余式,而φi(αi)=0,故如式(5)。Si=r(αi)=bi(αi)(5)联立式(1)与式(5),得到式(6)。Si=e(αi)(6)从式(6)可以看出,伴随式S仅仅与错误图样e(x)有关。2.2计算错误位置多项式假设错误图样e(x)有v个错误,并且错误位置分布在xj1,xj2,……,xjv,其中0≤j1<j2<……<jv<n,即式(7)。作者简介:李璜宁,上海航天电子有限公司,硕士;研究方向:信息与通信工程。收稿日期:2022-12-05;修回日期:2022-12-23。摘要:阐述太空中的恶劣环境影响,数据在存储传输过程中因为诸如单粒子效应而产生的错误,需要对于数据接收端接收到的可能存在错误数据进行检查以及纠错,用以保证数据结构的完整性与可靠性。在诸多检纠错码中,BCH码无疑是一种较为成熟的方案,探讨一种较为新型的BCH码译码方案,完成对于给定长度的数据进行译码,从而完成检错、纠错过程。关键词:信息通信,FPGA,BCH,译码。中图分类号:TN975,TN792文章编号:1674-2583(2023)01-0004-04DOI:10.19339/j.issn.1674-2583.2023.01.002文献引用格式:李璜宁,刘小荣....