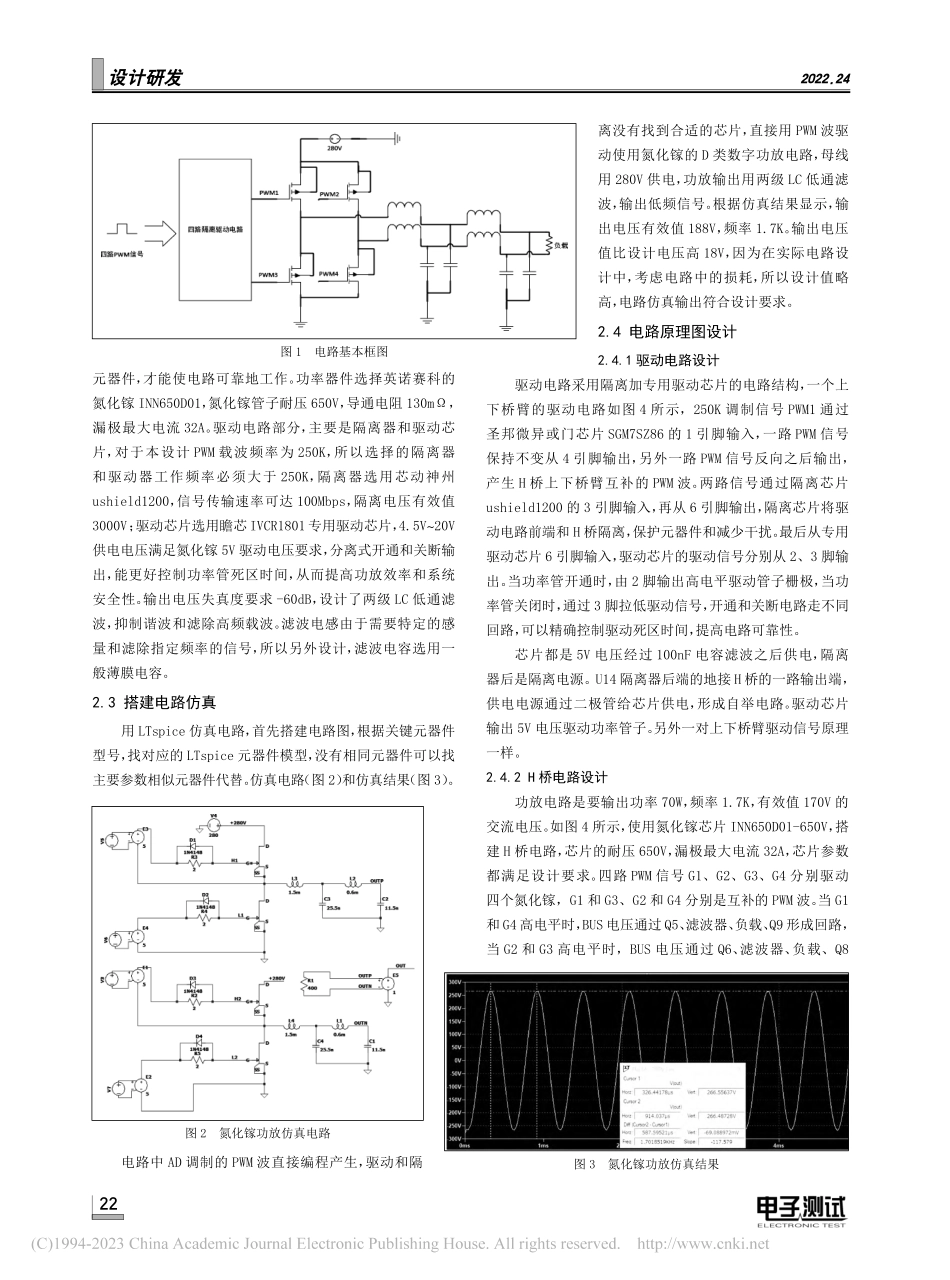

设计研发2022.24210引言目前,硅MOS管作为功率器件,在数字D类功放电路中应用非常多。然而,由于对高速、高温和大功率半导体器件需求的不断增长,使得半导体业重新考虑半导体所用设计和材料。随着多种更快、更小应用设备的不断涌现,硅材料已难以维持摩尔定律,使宽禁带半导体功率器件得到迅速发展[1]。宽禁带半导体被称为第三代半导体材料,是指禁带宽度大于2.3eV的半导体材料,其材料包括:A1N,GaN,BN,SiC,ZnO,金刚石等[2-3]。本文使用的氮化镓功率器件具备高频、高效、高功率、耐高压、耐高温、抗辐射能力强等优越性能,并可与成本极低、技术成熟度极高的硅基半导体集成电路工艺相兼容,在新一代高效率、小尺寸的5G通讯、新能源汽车、工业电源等领域具有巨大的发展潜力。1氮化镓数字D类功放电路原理数字D类功放电路采用氮化镓作为功率器件,具有高开关频率、低导通电阻和易驱动等特点[4]。数字D类功放电路原理:首先,把四路PWM信号通过隔离器,将驱动低压信号和功放输出的高压信号隔离,减少低压信号受到干扰,再通过专用驱动芯片驱动氮化镓,驱动芯片分离式输出,可单独调节开通电阻和关断电阻,精准控制驱动信号的死区时间[5],从而提高功放效率和保证电路安全性;其次,采用H桥式电路,使四个氮化镓管子分别接四路驱动信号,让上下桥臂氮化镓管子驱动信号互补;最后,输出差分信号与滤波电路连接,滤波电路滤掉高频载波,输出需要的基波信号。2应用电路原理图设计2.1电路组成框图设计包括驱动电路、功放电路和滤波电路,输出70W功率,有效值170V的1.7K交流信号。下图1为本系统框图,采用AD调制方式的PWM波,驱动数字D类功放,直流供电电压280V,将需要的弱信号功率放大。调制频率为250K,调制率为95%,基波信号1.7K。隔离器将强电和弱电隔离,很好地保护弱电部分。用专用的驱动芯片驱动氮化镓管子,输出用两级LC低通滤波。2.2关键器件选型电路有三个主要组成部分,每一部分都需要选择合适的基于氮化镓的数字D类功放电路设计与实现杨通元(中国振华(集团)科技股份有限公司,贵州贵阳,550018)摘要:本文介绍一种基于氮化镓芯片设计的数字D类功放电路。通过使用开关速度快、寄生参数小、电气性能优越的氮化镓作为功率器件,设计一个数字D类功放电路,放大信号功率,用于检测轨道上是否有列车占用的信息。实验结果表明,高频载波通过功放器将信号功率放大,再通过LC低通滤波,输出低频解调信号,实测解调信号失真度小于-60dB,验证了该...