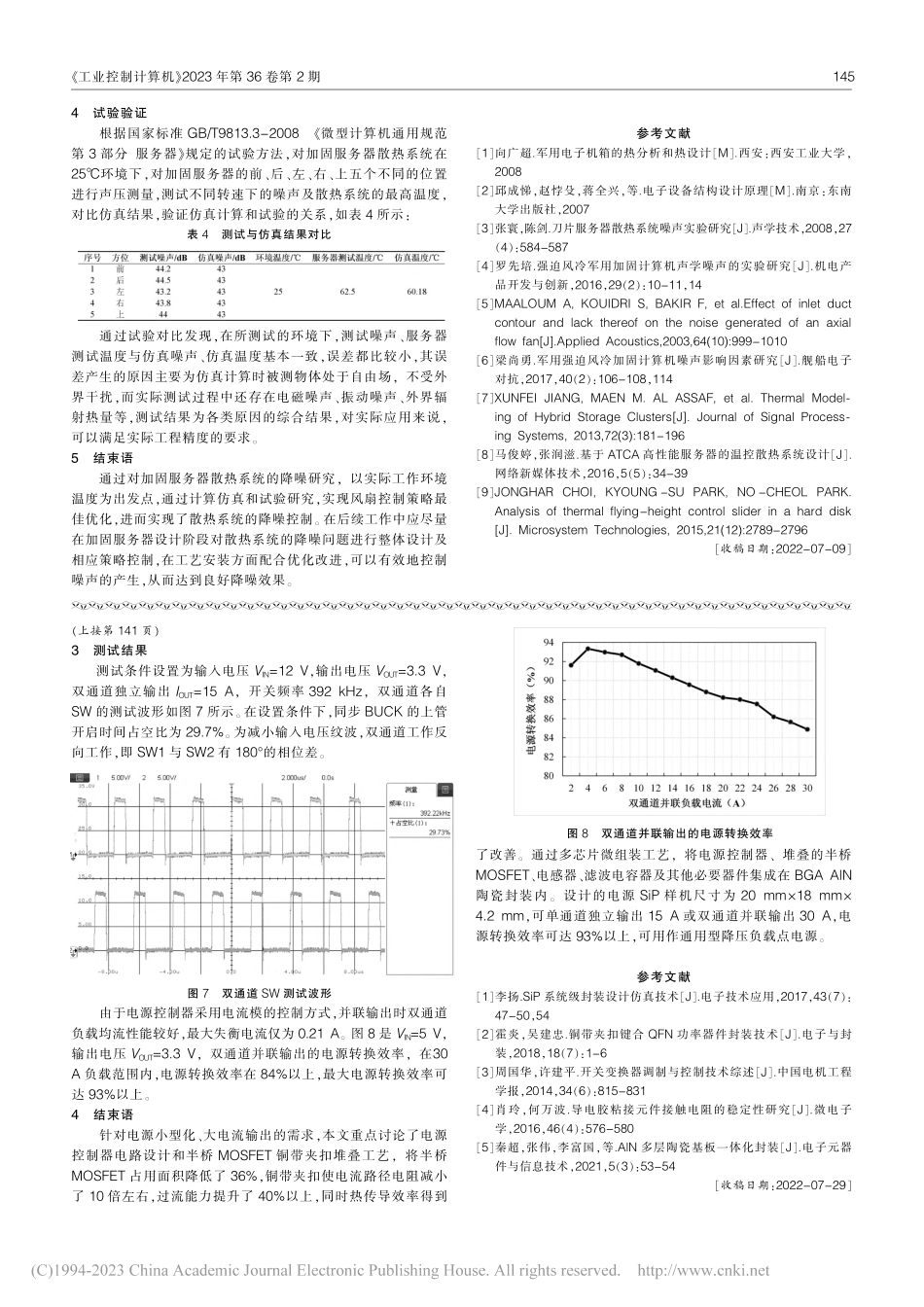

*重庆博士后研究项目特别资助1同步BUCKDC-DC电源简介随着FPGA、CPU、GPU等高性能运算器件的晶体管集成规模和工作频率不断提高,大电流输出的电源需求增长迅猛。同时,整机系统轻便化趋势对电源的尺寸要求越来越高。实现电源小型化的有效方法之一是采用系统级封装(SysteminPackage,SiP)设计,将多个集成电路裸芯片及其他必要元器件集成于同一封装体内,实现完整的电源功能。相较于基于分立器件设计的电源,电源SiP具有尺寸小、成本低、易于系统应用的优点[1]。为满足大电流电源产品小型化的要求,本文设计了一种同步BUCKDC-DC电源SiP。如图1所示,同一封装内集成的器件包括电源控制器、高/低边半桥功率开关MOSFET、电感器、电压/电流反馈、反馈补偿电路及其他无源器件。其中半桥MOS-FET采用铜带夹扣堆叠的工艺集成,提高封装效率,降低电流路径电阻,改善热传导性能[2]。图1同步BUCKDC-DC电源示意图2电源SiP设计本文通过半桥MOSFET铜带夹扣堆叠、系统级封装集成设计,实现高效率、小尺寸、双通道同步BUCKDC-DC电源SiP样品。其负载能力为单路独立15A/双路并联30A,以满足大电流应用。2.1电源控制器电路设计同步BUCK电源拓扑电源控制器集成了高、低边MOSFET驱动,支持双通道、多相、电流模式控制等操作。同步BUCKDC-DC电源的输出电压VOUT由图1中的分压电阻RH、RL和内部的0.6V基准决定:VOUT=0.6×RH+RLRL(1)控制器采用峰值电流模式控制电源输出,易于实现电源的过流保护,多路并联的负载均流[3]。图1中的R1、R2、C1为Type-II型环路补偿电路,以消除BUCKDC-DC连续电流模式下高边管QH导通占空比大于50%时产生的次谐波振荡。如图2所示,电感器的直流电阻RDCR被用作电流检测元件。相对于使用电流采样电阻,此方法既能减小器件占用面积,有助于电源SiP的小型化;又能减小电流路径导通损耗,提升电基于半桥MOSFET芯片铜带夹扣堆叠的电源SiP设计*康丙寅易文双方亚洲张颖(中国电子科技集团公司第二十四研究所,重庆400060)DesignofPowerSiPBasedonCopperClipStackedHalf-bridgeMOSFETs摘要:采用系统级封装(SysteminPackage,SiP)设计是实现电源小型化的有效方式之一。同步BUCKDC-DC变换器中的半桥功率开关MOSFET,通过堆叠工艺利用纵向空间,将芯片的占用面积降低了36%。MOSFET芯片表面做焊锡浸润材料金属化处理,直接与铜带夹扣锡膏烧焊,将电流路径电阻减小了约10倍,同时热传导效率得到了改善。通过多芯片微组装工艺,将电源控制器、MOSFE...