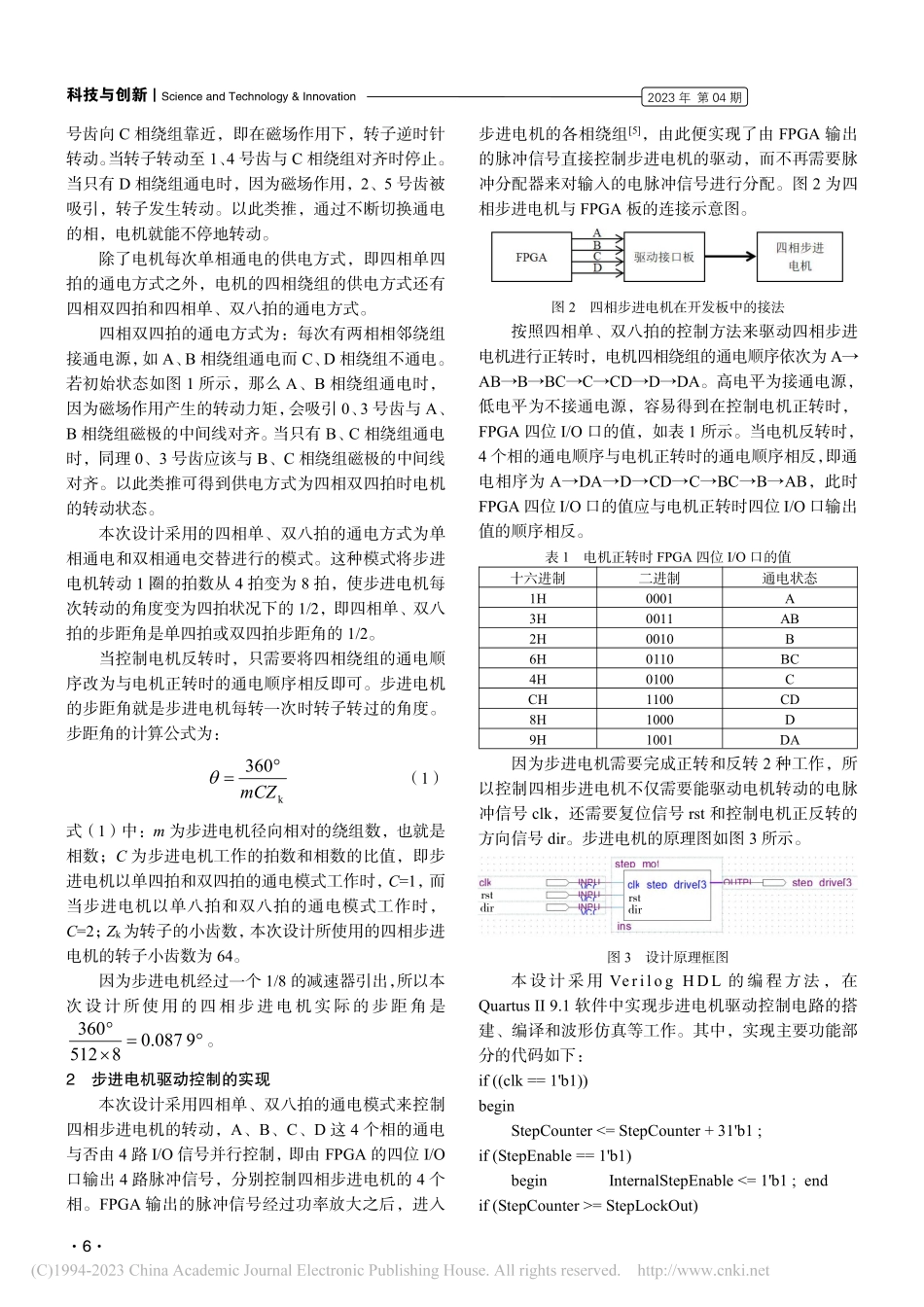

ScienceandTechnology&Innovation┃科技与创新2023年第04期·5·文章编号:2095-6835(2023)04-0005-03基于HDL/FPGA的步进电机驱动控制器设计*段简1,张奕婷1,郑晓峰1,陈磊1,周颖1,钱敏1,2(1.苏州城市学院电子信息工程系,江苏苏州215104;2.苏州大学电子信息学院电子科学与技术系,江苏苏州215006)摘要:步进电机可以把输入的电脉冲信号转换为离散的机械运动,FPGA被作为核心器件来实现对步进电机的驱动控制。通过使用VerilogHDL,设计一个步进电机的驱动控制电路;使用QuartusII软件,实现对四相步进电机驱动控制程序的编译和仿真验证驱动程序的功能;通过波形仿真对程序进行分析,验证输出波形是否满足控制系统的需要。最终下载测试表明,所设计的控制系统能够完整地实现四相步进电机正转、反转和复位功能。关键词:步进电机;驱动控制器;EDA;VerilogHDL中图分类号:TP311文献标志码:ADOI:10.15913/j.cnki.kjycx.2023.04.002步进电机是一种应用范围广泛的驱动控制装置,其工作原理是将输入的电脉冲信号进行转换,使自身产生相对应的角位移或者线位移[1-2]。步进电机的角位移量或线位移量与步进电机接收到的脉冲数成正比,即输入的脉冲信号越多,步进电机的角位移或线位移就越多。而步进电机的转速则由输入脉冲的频率控制,输入的电脉冲信号的频率越高,步进电机的转速就越快。步进电机根据结构的不同,主要可以分为3种类型,即反应式(VR)、永磁式(PM)和混合式(HS)[3]。本次设计所采用的步进电机是四相反应式步进电机,其示意图如图1所示。图1四相反应式步进电机与传统设计方法相比,采用基于硬件描述语言/现场可编程门阵列HDL/FPGA(HardwareDescriptionLanguage,FieldProgrammableGateArray)的EDA(ElectronicDesignAutomation)设计方法设计数字系统有巨大的优越性,且已成为大规模集成电路设计中使用最广泛的一种方法。在控制驱动步进电机时,由于步进电机能直接接收数字量的输入来控制电脉冲,且电路设计比较简单,适宜采用HDL/FPGA实现;通过FPGA开发工具QuartusⅡ可以高效地进行编译综合、波形仿真、下载测试,从而能够简化设计、提升效率、实现功能模块化[3-4]。1步进电机的工作原理和驱动方式如图1所示,步进电机主要由2部分组成:一个是定子,上面有几组缠绕着线圈的齿;另一部分是可自由转动的转子。定子有4相绕组,转子上一共有6个齿。以电机的四相单四拍的通电模式为例,反应式步进电机的工作原理是利用了物理...