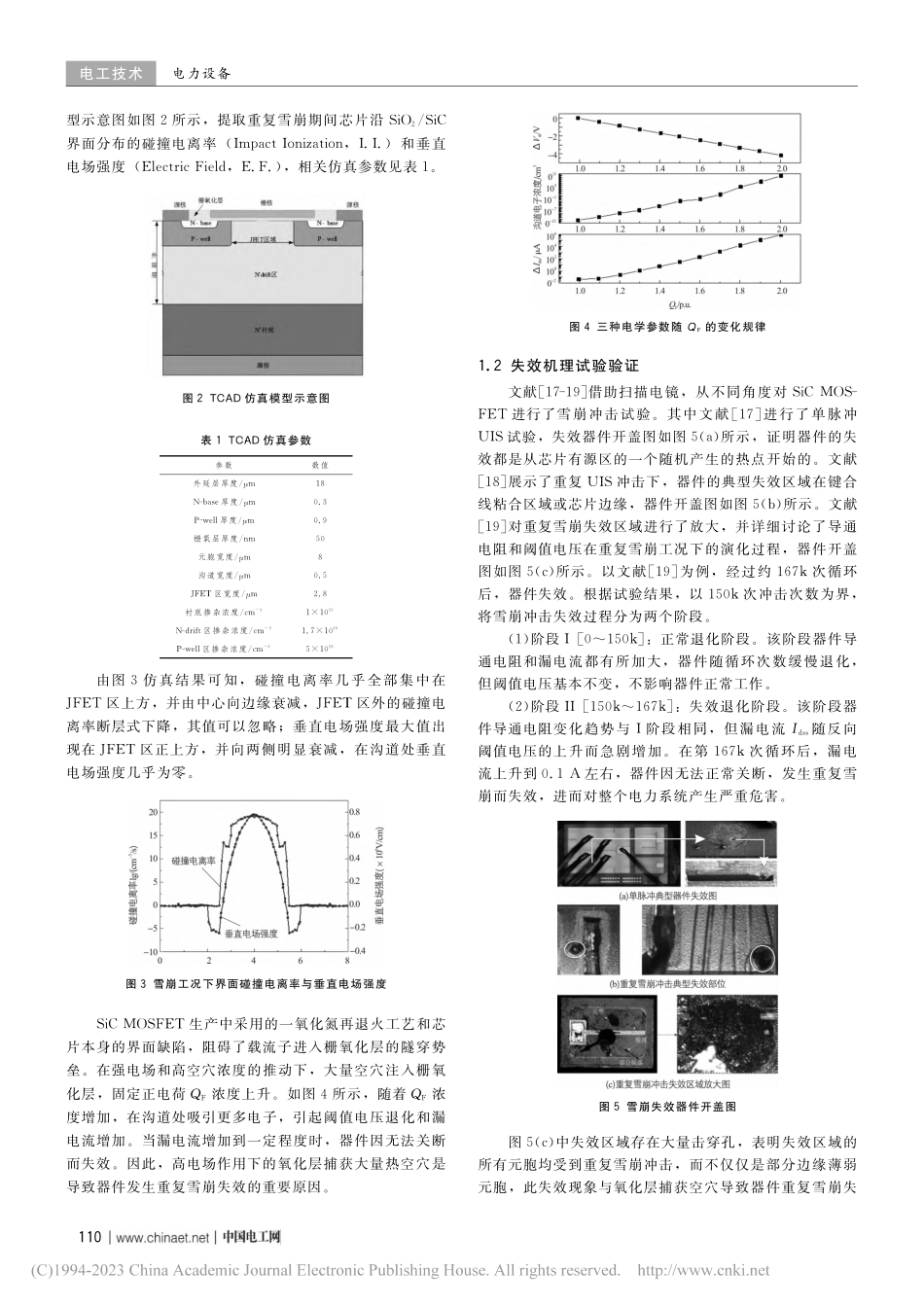

SiCMOSFET重复雪崩能力提升的芯片结构优化方法*朱哲研2,李辉2,姚然1,2*,刘人宽2,陈中圆1,李尧圣1(1.先进输电技术国家重点实验室,北京智慧能源研究院,北京102209;2.输配电装备及系统安全与新技术国家重点实验室(重庆大学),重庆400044)摘要:SiCMOSFET的高速开关工况易诱发巨大的di/dt,从而在电路的感性负载上引发过电压,导致器件进入雪崩状态。在多次雪崩冲击后,器件易发生重复雪崩失效。针对SiCMOSFET芯片元胞结构中栅氧化层薄弱导致器件耐重复雪崩冲击能力较差的问题,进行芯片元胞结构优化研究,以增强芯片耐重复雪崩能力,提升器件可靠性。首先,研究SiCMOSFET器件重复雪崩失效机理,开展SiCMOSFET器件重复雪崩失效测试,基于失效测试结果建立SiCMOSFET重复雪崩失效可靠性评估模型;其次,针对SiCMOSFET芯片元胞结构提出了栅极底部蚀刻、P-well区扩展、JFET顶部削弱三种优化结构,并研究三种优化结构对SiCMOSFET芯片SiO2/SiC界面处碰撞电离率和垂直电场强度的影响;最后,基于SiCMOSFET雪崩失效可靠性评估模型,对比分析了三种不同优化结构SiCMOSFET的可靠性。研究结果表明SiCMOSFET器件栅极蚀刻元胞结构具有更高的重复雪崩失效可靠性,相关研究成果为SiCMOSFET器件耐重复雪崩失效能力提升的芯片元胞设计奠定理论基础。关键词:SiCMOSFET;重复雪崩失效;失效模型;失效机理;可靠性中图分类号:TM56DOI:10.19768/j.cnki.dgjs.2023.04.032ChipStructureOptimizationMethodforImprovingRepetitiveAvalancheCapabilityofSiCMOSFET*ZHUZheyan2,LIHui2,YAORan1,2*,LIURenkuan2,CHENZhongyuan1,LIRaosheng1(1.StateKeyLaboratoryofAdvancedPowerTransmissionTechnology,BeijingInstituteofSmartEnergy,Beijing102209,China;2.StateKeyLaboratoryofPowerTransmissionEquipment&S...