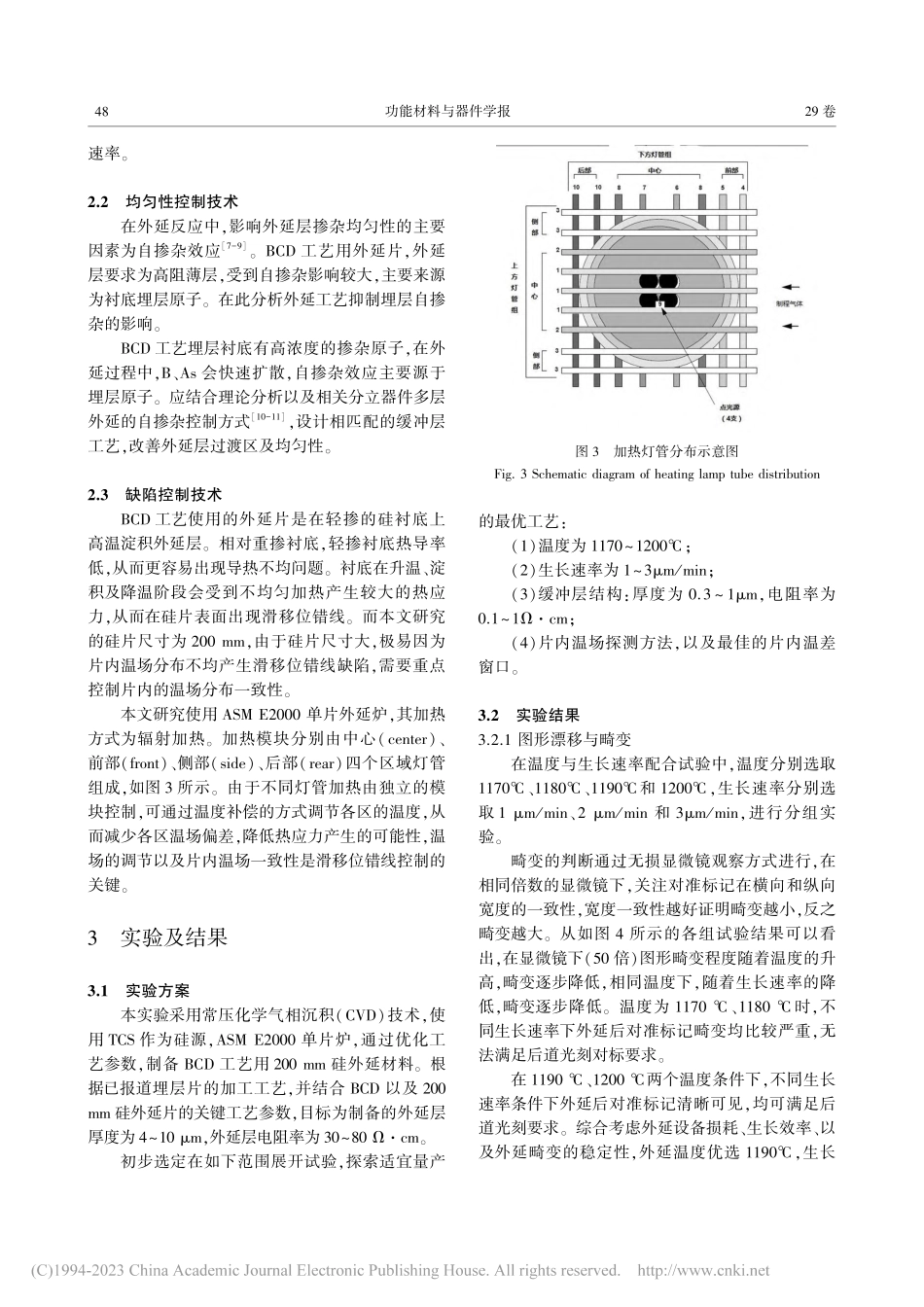

第29卷第1期功能材料与器件学报Vol.29,No.12023年2月JOURNALOFFUNCTIONALMATERIALSANDDEVICESFeb.,2023文章编号:1007–4252(2023)01–0001–046DOI:10.20027/j.gncq.2023.0001收稿日期:2022-07-26;修订日期:2023-02-19作者简介:仇光寅,(1986年-),男,江苏南京人,博士,工程师,现从事半导体材料的研发和制备(E-mail:qiuguangyin@gs-epi.com).200mmBCD器件用硅外延片制备技术研究仇光寅∗,刘勇,邓雪华,杨帆,金龙(南京国盛电子有限公司,江苏省南京市211111)摘要:本文涉及200mmBCD(Bipolar-CMOS-DMOS)器件用硅外延片制备技术,通过结合BCD工艺用外延材料的特性要求,从外延图形漂移、外延层均匀性、表面缺陷等参数指标,分析了衬底埋层浓度、生长温度、生长速率、缓冲层结构等工艺参数对外延参数的影响,优化了BCD工艺用硅外延片的制备方法。本文采用常压化学气相沉积(CVD)技术制备了BCD工艺用200mm硅(Si)外延材料,通过Hg-CV、SP1及SRP对埋层外延片进行测试分析,实验结果验证了工艺设计的正确性和有效性,提升了大尺寸埋层外延制备技术的产业化水平。关键词:埋层外延;高阻薄层;图形漂移;自掺杂;表面缺陷中图分类号:TB34文献标识码:AStudyon200mmSiliconEpitaxyPreparationTechnologyforBCDProcessQiuGuangyin∗,LiuYong,DengXuehua,YangFang,JinLong(NanjingGuoshengElectronicsCO.,LTD.,Nanjing,211111,China)Abstract:Focusingon200mmsiliconepitaxypreparationtechnologyforBCDdevices,basedonthepropertiesofepitaxiallayersuchaspatternshift,uniformityandsurfacedefects,theinfluencingfactorsoftheprocesssuchasconcentrationofburie...