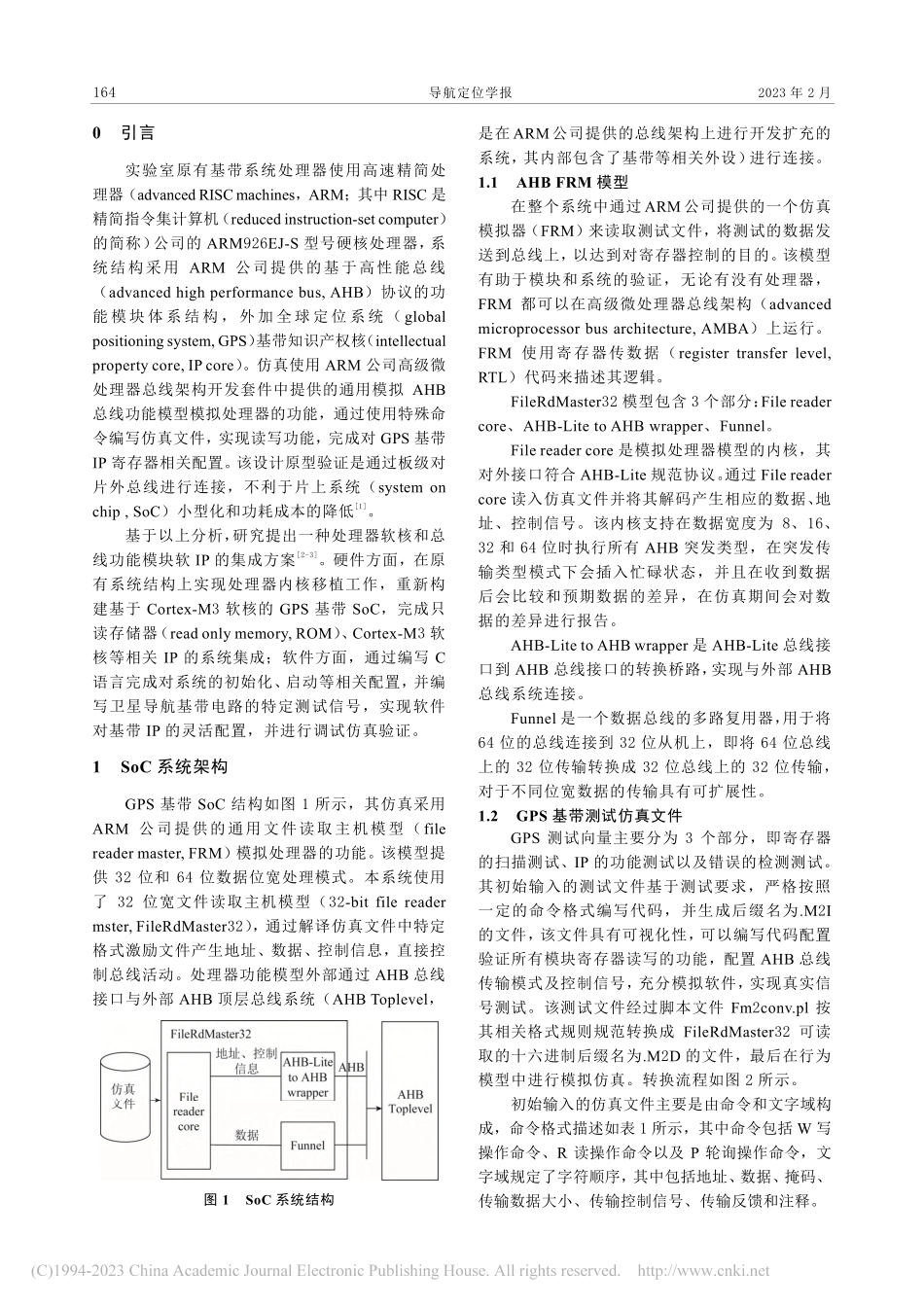

第11卷第1期导航定位学报Vol.11,No.12023年2月JournalofNavigationandPositioningFeb.,2023引文格式:赵继彬,黄海生,李鑫,等.GPS基带SoC中软硬协同设计[J].导航定位学报,2023,11(1):163-169.(ZHAOJibin,HUANGHaisheng,LIXin,etal.SoftwareandhardwarecooperativedesigninGPSbasebandSoC[J].JournalofNavigationandPositioning,2023,11(1):163-169.)DOI:10.16547/j.cnki.10-1096.20230125.GPS基带SoC中软硬协同设计赵继彬,黄海生,李鑫,朱振兴(西安邮电大学电子工程学院,西安710121)摘要:针对ARM公司的ARM926EJ-S型号硬核形式固化处理器构建的全球定位系统(GPS)L1波段(中心频率为1575.42MHz)信号基带处理的片上系统(SoC)功耗高、成本高的问题,提出一种基于Cortex-M3开源软核处理器构建的GPS基带SoC系统,以实现处理器核的系统移植:针对软件实现和硬件实现的特点,完成基带处理的软硬件功能划分与协同设计;硬件部分选用Cortex-M3软核和高级微处理器总线架构2.0(AMBA2.0)片上总线为核心进行基带处理SoC架构设计,通过修改ARM公司提供的总线功能模块的软知识产权核(IPcore),构建高级高性能总线(AHB)和外围总线(APB)的总体结构,设计若干符合AMBA2.0协议的IP核,并完成基带等相关IP核的挂接,实现SoC系统功能的扩充;软件部分通过C语言完成对系统的初始化、启动等相关配置,并编写卫星导航基带电路的特定测试信号,实现软件对基带IP的灵活配置。仿真结果表明,该系统能够实现对基带IP的灵活配置,满足对器件的低功耗、微集成要求。关键词:Cortex-M3处理器;微处理器总线架构;片上系统;知识产权核;软硬件协调设计中图分类号:P228文献标志码:A文章编号:2095-4999(2023)01-0163-07SoftwareandhardwarecooperativedesigninGPSbasebandSoCZHAOJibin,HUANGHaisheng,LIXin,ZHUZhenxing(SchoolofElectronicEngineering,Xi’anUniversityofPostandTelecommunication,Xi’an710121,China)Abstract:Aimingattheproblemsofhighpowerconsumptionandhighcostofthesystemonchip(SoC)oftheglobalpositioningsystem(GPS)L1band(centerfrequency:1575.42MHz)signalbasebandprocessingconstructedbytheARM926EJ-Shardcoresolidcoreprocessor,aGPSbasebandSoCsystembasedontheCortex-M3open-sourcesoftcoreprocessorplannedbyARMDesignStartwasproposedtorealizethesystemtransplantationofthecore:accordingtothecharacteristicso...