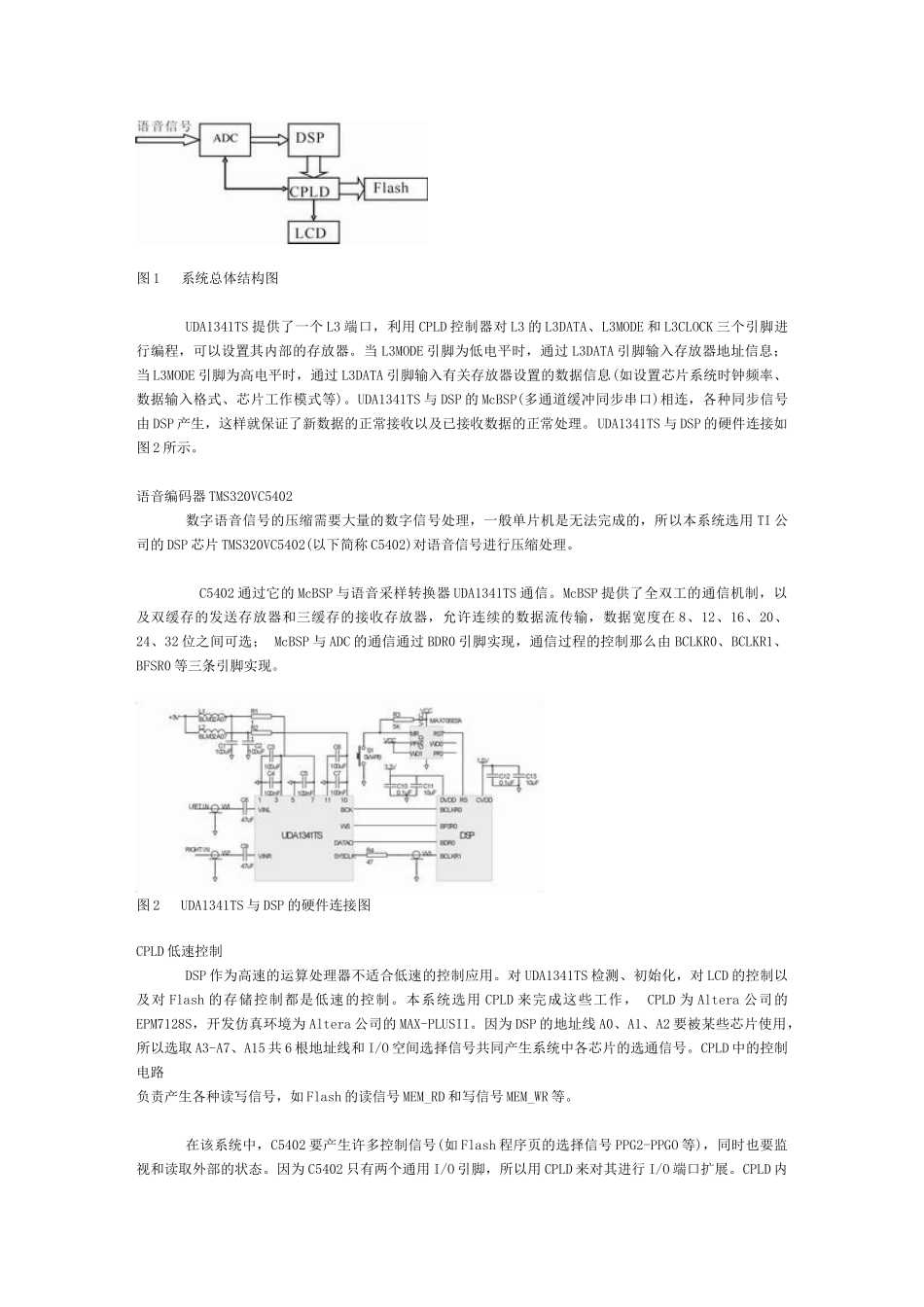

基于MPEG-2算法的列车语音记录设备摘要:本文介绍了一种新型列车语音记录设备的系统架构、特点和软硬件实现方法。运用DSP技术对语音信号进行处理、压缩和记录,实现了机车语音联控和列车当前状态信息的记录,进而标准乘务员的工作用语并协同监控装置分析行车故障关键词:A/D转换;语音数据编码;循环冗余校验前言列车运行监控记录装置在铁路的安全运输过程中发挥了巨大的作用,但缺乏的是没有语音记录功能。为了解决这个问题,按照铁道部的技术要求,本文研究开发了一种新型列车语音记录设备。该设备主要用于对乘务员机车联控进行录音,并可协同监控装置分析行车事故,为机务部门和运输部门的科学管理提供新的技术手段。鉴于常见设备的技术指标及标准,对于语音的数字化,以16KHz的采样频率、16位量化精度进行采样,在编码方面,采用MPEG-2压缩编码方式。硬件系统组成该语音记录设备如图1所示,整个系统由ADC、DSP、CPLD控制器、Flash大容量存储器及LCD显示屏等组成。在本系统中,ADC用来完成信号的转换,数据格式在16、18、20位之间可选,DSP为系统的核心数字处理器,功能强大,完成数字信号的压缩编码,CPLD用于数据传送的控制以及对ADC、Flash和LCD显示屏等器件的初始化检测设置,Flash用来存储数据,LCD显示屏用来显示当前系统的状态,如运行等待和数据处理等。系统上电后,假设有语音信号,那么输入ADC,得到一串数字信号送入DSP进行数据压缩编码,经过压缩编码的数据由CPLD存储到Flash中,整个系统以流水线的方式工作,数据的采集、压缩编码和存储同时进行。A/D转换器UDA1341TSUDA1341TS是由Philips公司生产的一款单片立体声A/D、D/A转换器,工作电压为3.0V,信噪比为97dB,具有双通道输入功能,采样频率在16,32和44.1KHz之间可选。UDA1341TS与DSP构成语音信号采集系统,主要涉及到位采样时钟(BCK)、字同步时钟(WS)、采样数据输出(DATAO)、系统时钟输入(SYSCLK)这几个对时序有要求的引脚。系统中,DATAO作为输出引脚,与DSP的BDR0引脚相连;BCK、WS、SYSCLK作为输入引脚,其时序由DSP供应。UDA1341TS的系统时钟只能是256Fs、384Fs、512Fs,通过对状态存放器的SC0位和SC1位编程可实现系统时钟的选择设置。这里Fs是语音信号的采样频率。在采样数据时,WS用来指明UDA1341TS的DATAO输出的有效数据。当系统对VINL(左声道)端口进行采样时,WS的上升沿说明一帧数据的起始,下降沿说明一帧数据的结束;当系统对VINR(右声道)端口进行采样时,WS的下降...